- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361317 > QS5LV931-66Q (QUALITY SEMICONDUCTOR INC) 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數(shù)資料

| 型號(hào): | QS5LV931-66Q |

| 廠商: | QUALITY SEMICONDUCTOR INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封裝: | QSOP-20 |

| 文件頁(yè)數(shù): | 3/8頁(yè) |

| 文件大?。?/td> | 62K |

| 代理商: | QS5LV931-66Q |

3

INDUSTRIAL TEMPERATURE RANGE

QS5LV931

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

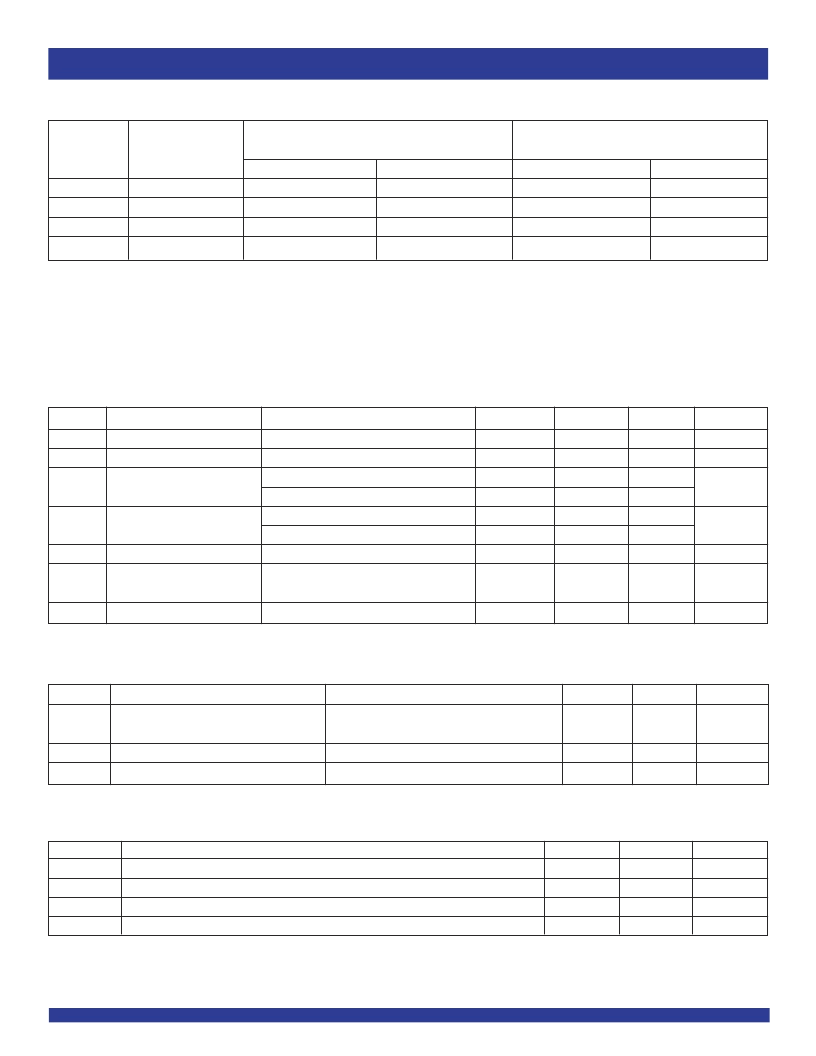

POWER SUPPLY CHARACTERISTICS

Symbol

Parameter

I

DDQ

Quiescent Power Supply Current

Test Conditions

Typ.

—

Max.

1

Unit

mA

V

DD

= Max., OE/

RST

= LOW,

SYNC = LOW, All outputs unloaded

V

DD

= Max., V

IN

= 3V

V

DD

= Max., C

L

= 0pF

I

DD

I

DDD

Power Supply Current per Input HIGH

Dynamc Power Supply Current per Output

1

30

0.3

μ

A

0.2

μ

A/MHz

FREQUENCY SELECTION TABLE

SYNC (MHz)

(allowable range)

(1)

Output Used for

Feedback

Q/2

Q

0

-Q

4

Q/2

Q

0

-Q

4

Output Frequency Relationships

Q/2

SYNC

SYNC / 2

SYNC

SYNC / 2

FREQ_SEL

HIGH

HIGH

LOW

LOW

Min.

F

MIN_Q/2

F

MIN_Q

F

MIN_Q/2

/2

F

MIN_Q

/2

Max

Q

0

- Q

4

SYNC X 2

SYNC

SYNC X 2

SYNC

F

MAX _Q/2

F

MAX _Q

F

MAX _Q/2

/2

F

MAX _Q

/2

NOTE:

1. Operation in the specified SYNC frequency range guarantees that the VCO will operate in its optimal range of 20MHz to F

MAX_Q

x2. Operation with Sync inputs outside specified

frequency ranges may result in out-of-lock outputs. FREQ_SEL only affects VCO frequency and does not affect output frequencies.

DC ELECTRICAL CHARACTERISTICS OV ER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: T

A

= –40°C to +85°C, AV

DD

/V

DD

= 3.3V ± 0.3V

Symbol

V

IH

V

IL

V

OH

Parameter

Input HIGH Voltage

Input LOW Voltage

Output HIGH Voltage

Conditions

Min.

2

—

Typ.

—

—

—

—

—

—

100

—

Max.

—

0.8

—

—

0.45

0.2

—

5

Unit

V

V

V

Guaranteed Logic HIGH Level

Guaranteed Logic LOW Level

I

OH

=

24mA

I

OH

=

100

μ

A

V

DD

= Mn., I

OL

= 24mA

V

DD

= Mn., I

OL

= 100

μ

A

V

DD

— 0.6

V

DD

— 0.2

—

—

—

—

V

OL

Output LOW Voltage

V

V

H

I

OZ

Input Hysteresis

Output Leakage Current

—

mV

μ

A

V

OUT

= V

DD

or GND,

V

DD

= Max., Outputs Disabled

AV

DD

= Max., V

IN

= AV

DD

or GND

I

IN

Input Leakage Current

—

—

5

μ

A

INPUT TIMING REQUIREMENTS

Symbol

t

R

, t

F

Maximuminput rise and fall times, 0.8V to 2V

F

I

Input Clock Frequency, SYNC

(1)

t

PWC

Input clock pulse, HIGH or LOW

(2)

D

H

Duty Cycle, SYNC

(2)

Description

(1)

Min.

—

2.5

2

25

Max.

3

F

MAX _Q

—

75

Unit

ns

MHz

ns

%

NOTES:

1. See Output Frequency and Frequency Selection tables for more detail on allowable SYNC input frequencies for different speed grades with different FEEDBACK and FREQ_SEL

combinations.

2. Where pulse witdh implied by D

H

is less than t

WPC

limt, t

WPC

limt applies

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QS5LV931-80Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931 | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV93150Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV93166Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV93180Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QS5LV93180Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-80Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5U12 | 制造商:ROHM 制造商全稱:Rohm 功能描述:2.5V Drive Nch+SBD MOS FET |

| QS5U12_1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:2.5V Drive Nch+SBD MOS FET |

| QS5U12TR | 功能描述:MOSFET N-CH 30V 2A TSMT5 RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。