- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376314 > RM7965 (PMC-Sierra, Inc.) 64-bit Microprocessors with Integrated L2 Cache and EJTAG PDF資料下載

參數(shù)資料

| 型號: | RM7965 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | 64-bit Microprocessors with Integrated L2 Cache and EJTAG |

| 中文描述: | 64位集成二級高速緩存和EJTAG微處理器 |

| 文件頁數(shù): | 1/2頁 |

| 文件大?。?/td> | 194K |

| 代理商: | RM7965 |

RM7935/RM7965

64-bit Microprocessors with Integrated L2 Cache and EJTAG

PMC-2030350, Issue 4

Copyright PMC-Sierra, Inc. 2003–2006

All rights reserved. Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use.

PRODUCT HIGHLIGHTS

New high performance MIPS64-compatible Instruction Set

Architecture with integrated L2 cache and EJTAG:

668, 750, 835 and 900 MHz operating frequency.

1890 Dhrystone 2.1 MIPS @ 900MHz.

Dual-issue superscalar 7-stage pipeline.

16 Kbyte, 4-way set associative L1 Instruction cache.

16 Kbyte, 4-way set associative L1 Data cache.

256 Kbyte, 4-way set associative L2 cache with industry best 5-

cycle access latency.

Fast Packet Cache to assists processing of packet data.

8K entry branch prediction table.

Fully associative 64-entry TLB with dual pages.

High-performance Floating Point Unit (IEEE 754).

Fixed-point DSP instructions such as Multiply/Add,

Multiply/Subtract, and 3 Operand Multiply.

High-performance system interface:

32-bit multiplexed address/data (SysAD) bus with RM7935.

64-bit SysAD with RM7965.

Multiple outstanding reads with out-of-order return.

1600 Mbyte/s peak throughput.

200 MHz maximum frequency using HSTL signaling on the SysAD

bus.

SysAD bus supports 1.5 V, 2.5 V, 3.3V I/O logic.

Processor clock multipliers 2, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7, 7.5, 8,

8.5, 9, 10, 11, 12, 13, 14, 15, 16, 17.

Integrated on-chip EJTAG capability.

A 64-entry dynamic Trace Buffer for use in real-time trace and

debug.

Two 32-bit virtually-addressed Watch registers.

Integrated performance counters:

2 independent 32-bit counters.

Counts over 30 processor events including miss predicted

branches.

Enables full characterization and analysis of application

software.

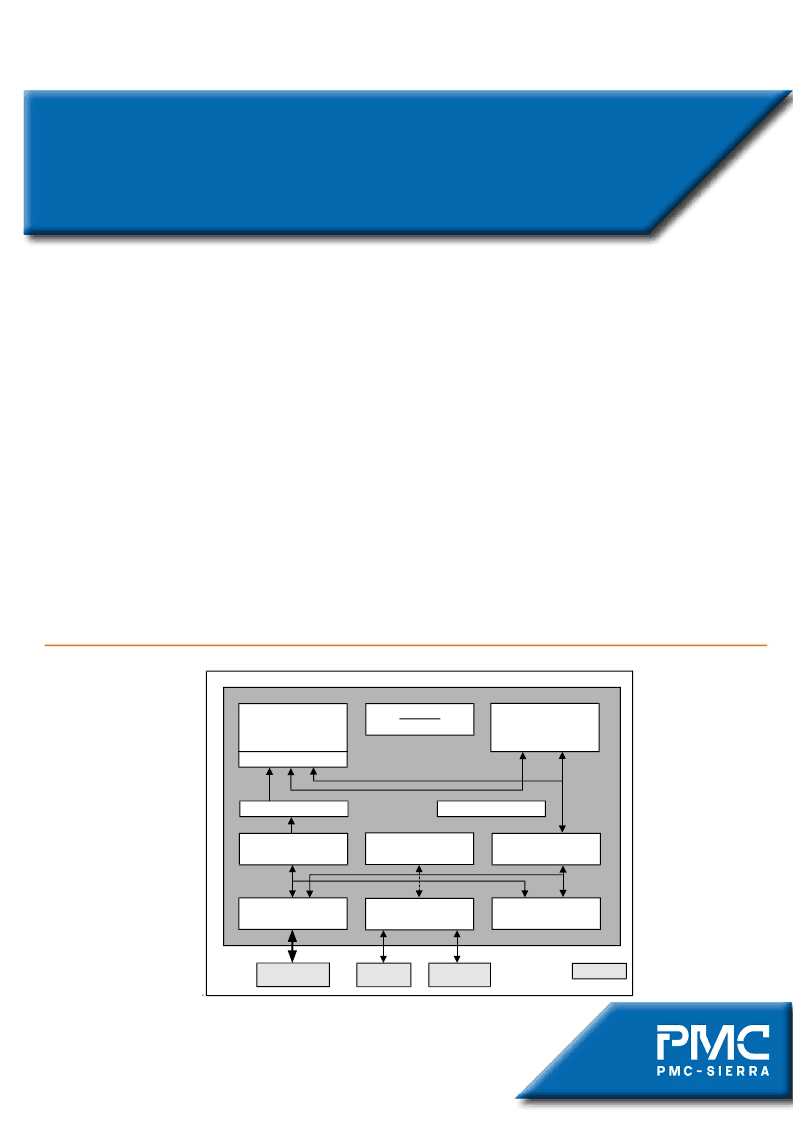

BLOCK DIAGRAM

Cache Test

Mode

64-bit Integer Unit

Dual-Issue Superscalar

Integer Multiplier

64-bit Floating Point Unit

Double/Single IEEE-754

Instruction Dispatch

8K Entry Branch History Tbl

Interface Unit

Secondary Cache

256 KB, 4-way

Line Lockable

System Control

Memory Manager

64-Entry, Dual Page

Data Cache

16 KB, 4-way

Line Lockable

Instruction Cache

16 KB, 4-way

Line Lockable

E9000 Core

SysAD

System Interface

Interrupt

Interface

Controller

On-Chip Debug

Branch Trace Buffer

PLL & Clock

Released

Product Brief

相關PDF資料 |

PDF描述 |

|---|---|

| RMLA3565-58 | Wideband Low Noise MMIC Amplifier |

| RMLA3565A-58 | Wideband Low Noise MMIC Amplifier |

| RN1102 | Isolated Resistor Termination Network |

| RN1102 | Switching, Inverter Circuit, Interface Circuit And Driver Circuit Applications |

| RN1111 | BUSSED RESISTOR NETWORK |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| RM7965-750TI-C001 | 制造商:PMC Sierra from Components Direct 功能描述:RM7965-750TI-C001 - Trays 制造商:PMC-Sierra 功能描述:PMC SIERRA RM7965-750TI-C001 Microprocessors |

| RM79LH1660-40 | 制造商:Esna Technologies 功能描述: |

| RM7M70202068362092LLP1 | 制造商:3M Electronic Products Division 功能描述:CABLE ASSEMBLY |

| RM7M70202068362200LLP1 | 制造商:3M Electronic Products Division 功能描述:CABLE ASSY |

| RM7M70202068362292LLP1 | 制造商:3M Electronic Products Division 功能描述:CABLE ASSEMBLY |

發(fā)布緊急采購,3分鐘左右您將得到回復。