- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373329 > RTC-65271 (愛普生(中國)有限公司) 8-Bit Real Time Clock Module(8位實時時鐘模塊) PDF資料下載

參數(shù)資料

| 型號: | RTC-65271 |

| 廠商: | 愛普生(中國)有限公司 |

| 英文描述: | 8-Bit Real Time Clock Module(8位實時時鐘模塊) |

| 中文描述: | 8位實時時鐘模塊(8位實時時鐘模塊) |

| 文件頁數(shù): | 2/2頁 |

| 文件大?。?/td> | 123K |

| 代理商: | RTC-65271 |

84

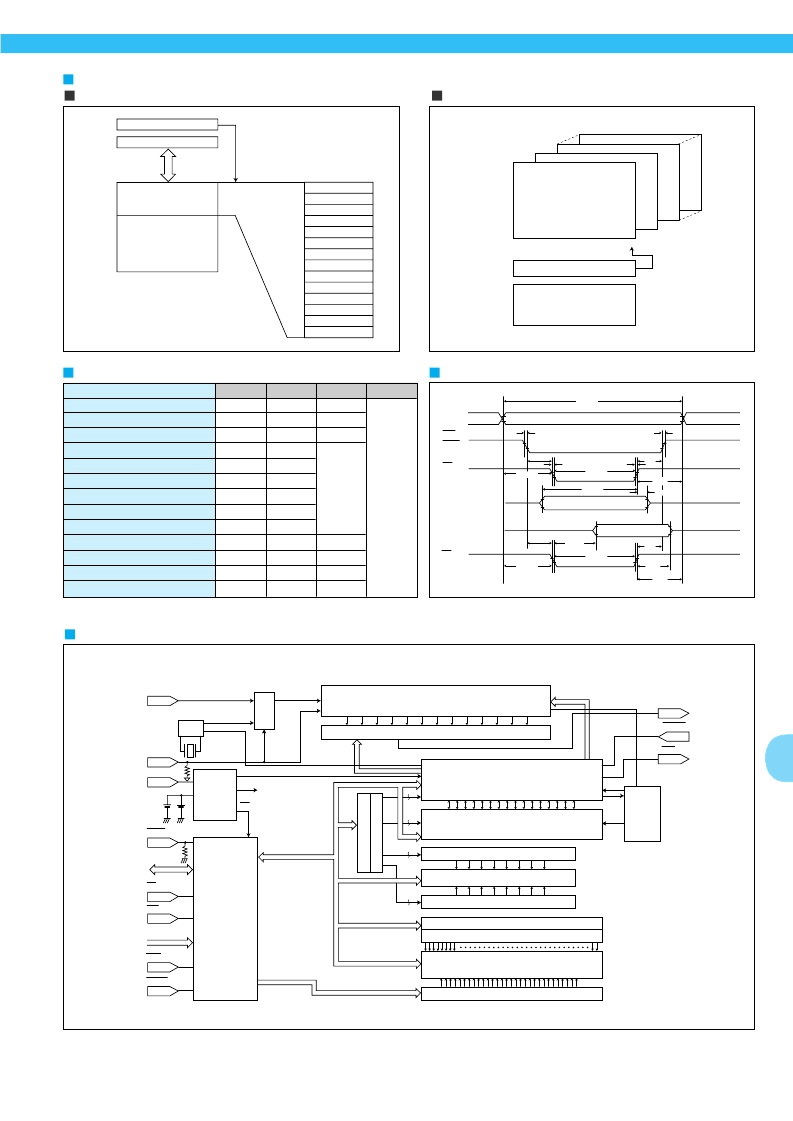

Real time clock module

INDIRECT ADDRESS REG

RTC DATA REGISTER

14-bytes

RTC

14-bytes

REAL TIME CLOCK

50-bytes

USER-RAM

INDIRECT

ADDRESS

00

00

00

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0D

0E

3F

3F

SECONDS

SECOND ALARM

MINUTES

MINUTE ALARM

HOURS

HOUR ALARM

DAY OF WEEK

DAY OF MONTH

MONTH

YEAR

REGISTER A

REGISTER B

REGISTER C

REGISTER D

128

OF 32-bytes

EXTENDED RAM

PAGES

PAGE 7F

02

01

PAGE 00

XRAM

XRAM PAGE REGISTER

XRAM + 1F

XRAM + 3F

XRAM + 20

XRAM + 21

THRU

THRU

ALIASES OF

PAGE REGISTER

A

0

to A

5

RTC

VALID

VALID

VALID

XRAM

WR

DATA BUS

WRITE

(D

O

to D

7

)

DATA

D(D

O

to D

7

)

RD

DATA BUS

READ

t

CYC

t

F

t

F

t

CWS

t

DSW

t

CH

t

AH

t

DHW

t

AWS

t

RWL

t

R

t

R

t

CRS

t

CH

t

DHR

t

AH

t

ARS

t

RWL

t

DDR

TCLOCK

TMODE

V

DD

BUS

INTERFACE

STBY

D

O

to D

7

RD

WR

A

0

to A

5

A

0

to A

4

RTC

XRAM

SELECTOR

50 %kHz

8.192

OSC

ON / OFF

POWER

SWITCHING

REFERENCE

POK

VPP

CE

DATA / CONTROL

DIVIDER CHAIN

13 TAPS TO SELECTOR

PERIODIC INTR / SQ WAVE SELECTOR

RS0 to RS3

D

R

4

10

1

3

3

REGISTERS

A,B,C,D

CLOCK, CALENDAR, AND ALARM

REGISTERS

COLUMN DECODER, 1 of 8

50-bytes USER-RAM

ROW DECODER, 1 of 8

ROW DECODER, 1 of 32

DV0 to DV2

SQW

RESET

IRQ

CLOCK

CALENDAR

UPDATE

EXTENDED RAM REGISTER

EXTENDED RAM

4096-bytes

COLUMN DECODER, 1 of 128

Switching characteristics

Item

Cycle Time

Pulse width RD

/WR

=

“

L

”

interval

Signal rise / fall time CS, RD

Address holding time

Address setup before RD

Address setup before WR

Chip select setup time before RD

Chip select setup time before WR

Chip select hold time a after RD

Read data holding time

RD

Peripheral output data delay time

Peripheral write data setup time

Timing chart

Address map

RTC address map

Block diagram

Extended RAM address map

(V

DD

= 5 V

±

10 %, GND =0 V, Ta = -10 to +70

°

C)

Symbol

t

CYC

t

RWL

t

R,

t

F

t

AH

t

ARS

t

AWS

t

CRS

t

CWS

t

CH

t

DHR

t

DHW

t

DDR

t

DSW

200

__

__

, WR

__

__

/WR

__

__

Min.

395

325

__

20

50

0

50

0

20

10

0

20

Max.

DC

__

30

100

__

240

__

Remarks

ns

__

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTC-6593 | REAL TIME CLOCK MODULE FOR PC/AT |

| RTC-72421A | Real-Time Clock |

| RTC-72421B | Real-Time Clock |

| RTC-72423A | Real-Time Clock |

| RTC-72421 | Real time clock module(4-bit REAL TIME CLOCK MODULE) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTC-6583 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Real-Time Clock |

| RTC-6587 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Real-Time Clock |

| RTC-6593 | 制造商:EPSON 制造商全稱:EPSON 功能描述:REAL TIME CLOCK MODULE FOR PC/AT |

| RTC-6597 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Real-Time Clock |

| RTC6601 | 制造商:Richwave 功能描述:SP3T SWITCH, DFN 2x2-8L |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。