- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378205 > RTC-8564JE (Electronic Theatre Controls, Inc.) I2C-BUS INTERFACE REAL TIME CLOCK MODULE PDF資料下載

參數(shù)資料

| 型號: | RTC-8564JE |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | I2C-BUS INTERFACE REAL TIME CLOCK MODULE |

| 中文描述: | I2C總線接口實(shí)時時鐘模塊 |

| 文件頁數(shù): | 2/2頁 |

| 文件大小: | 115K |

| 代理商: | RTC-8564JE |

70

Real time clock module

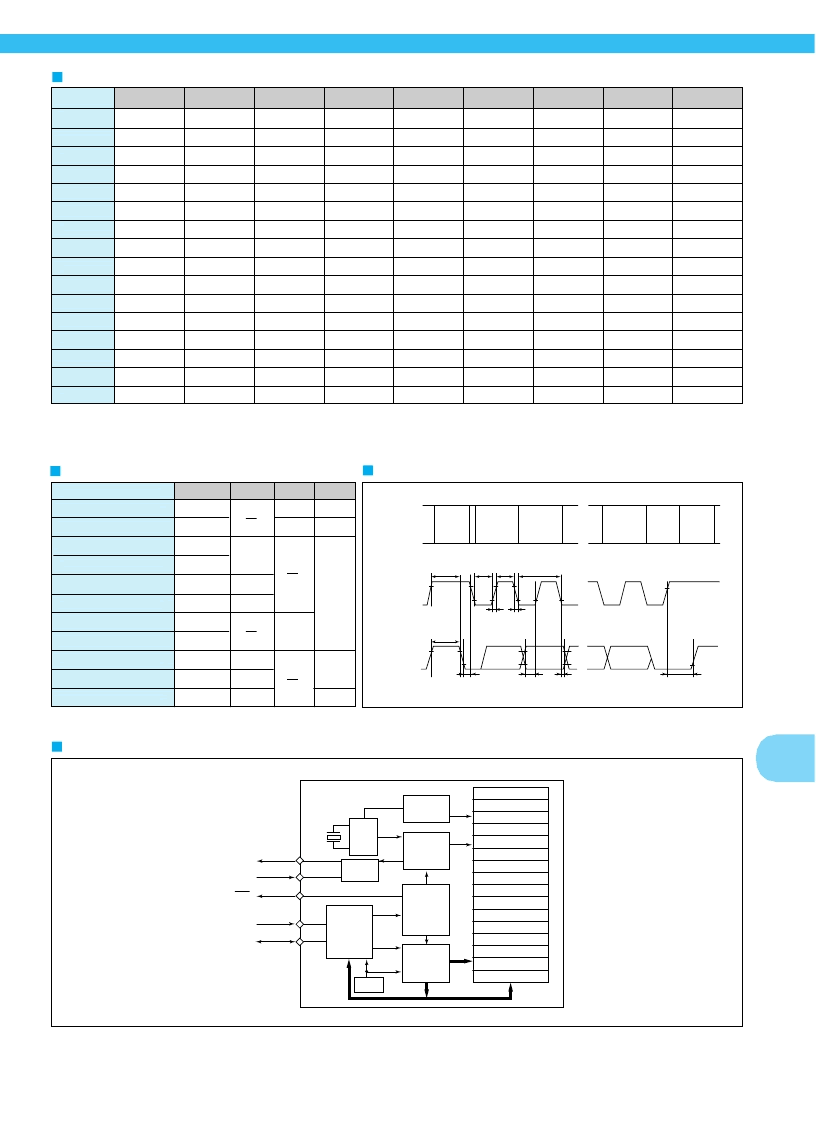

Switching characteristics

Block diagram

Register table

Timing chart

INT

SCL

SDA

CLKOUT

32.768 kHz

CRYSTAL

OSC

POR

Output

Control

Divider

Voltage

Detector

Control

Logic

Address

Register

Timer

Timer Control

CLKOUT frequency

Weekday Alarm

Day Alarm

Hour Alarm

Minutes Alarm

Years

Month/Century

Weekdays

Days

Hours

Minutes

Seconds

Control2

Control1

00

0F

I C-BUS

Interface

Protocol

Start

Condition (s)

Stop

Condition (P)

t

SU;STO

t

HD;DAT

t

HD;STA

t

SU;STA

t

LOW

t

HIGH

1/f

SCL

tr

tf

tBUF

t

SU;DAT

Bit 7

MSB (A7)

Bit6

(A6)

Bit0

LSB

(R/W)

ACK

(A)

SCL

SDA

CLKOE

0 : Always set this bit to

“

0

”

.

Address

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Register symbol

Control 1

Control 2

Sec

Min

Hour

Day

Week

Month/Century

Year

Minutes Alarm

Hours Alarm

Day Alarm

Week Alarm

CLKOUT frequency

Timer control

Timer

bit 7

TEST

0

VL

C

Year 80

AE

AE

AE

AE

FE

TE

128

bit 6

0

0

S 40

Min 40

Year 40

A-Min 40

A-Hr 40

64

bit 5

STOP

0

S 20

Min 20

Hour 20

Day 20

Year 20

A-Min 20

A-Hr 20

A-Day 20

32

bit 4

0

TI/TP

S 10

Min 10

Hour 10

Day 10

Month 10

Year 10

A-Min 10

A-Hr 10

A-Day 10

16

bit 3

TEST

AF

S 8

Min 8

Hour 8

Day 8

Month 8

Year 8

A-Min 8

A-Hr 8

A-Day 8

8

bit 2

0

TF

S 4

Min 4

Hour 4

Day 4

W 4

Month 4

Year 4

A-Min 4

A-Hr 4

A-Day 4

A-W 4

4

bit 1

0

AIE

S 2

Min 2

Hour 2

Day 2

W 2

Month 2

Year 2

A-Min 2

A-Hr 2

A-Day 2

A-W 2

FD1

TD1

2

bit 0

0

TIE

S 1

Min 1

Hour 1

Day 1

W 1

Month 1

Year 1

A-Min 1

A-Hr 1

A-Day 1

A-W 1

FD0

TD0

1

Item

SCL clock frequency

Tolerance spike time on bus

Start condition set-up time

Start condition Hold time

SCL

“

L

”

time

SCL

“

H

”

time

SCL and SDA rise time

SCL and SDA fall time

Date set-up time

Date hold time

Stop condition set-up time

Symbol

f

SCL

t

SW

t

SU

;

STA

t

HD

;

STA

t

LOW

t

HIGH

t

r

t

f

t

SU

;

DAT

t

HD

;

DAT

t

SU

;

STO

Min.

0.6

1.3

0.6

100

0

4.0

Max.

400

50

0.3

Unit

kHz

ns

μs

ns

μs

(V

DD

=1.8 to 5.5 V, Ta=-40

C to +85

C)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTC-8583 | I2C-BUS COMPATIBLE REAL TIME CLOCK MODULE |

| RTC-8593 | I2C-BUS COMPATIBLE REAL TIME CLOCK MODULE |

| RTC-8593SB | I2C-BUS COMPATIBLE REAL TIME CLOCK MODULE |

| RTC8583 | I2C-BUS COMPATIBLE REAL TIME CLOCK MODULE |

| RTC4553 | SERIAL-INTERFACE REAL TIME CLOCK MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTC-8564JE,(B) | 制造商:Epson Toyocom 功能描述:I2C-Bus Interface RTC Module VSOJ 20pin |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。