- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376330 > S12DTB128PIMV2 (Motorola, Inc.) MC9S12DT128 Device User Guide V02.09 PDF資料下載

參數(shù)資料

| 型號(hào): | S12DTB128PIMV2 |

| 廠商: | Motorola, Inc. |

| 英文描述: | MC9S12DT128 Device User Guide V02.09 |

| 中文描述: | MC9S12DT128設(shè)備的用戶手冊(cè)V02.09 |

| 文件頁(yè)數(shù): | 22/138頁(yè) |

| 文件大小: | 2083K |

| 代理商: | S12DTB128PIMV2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)

MC9S12DT128 Device User Guide — V02.09

22

–

Port K

Port K pull-up resistors are enabled out of reset, i.e. Bit 7 = PUKE = 1 in the register PUCR at

Base+$000C. Therefore care must be taken not to clear this bit.

–

Port M[1:0]

PM1:0 must be configured as outputs or their pull resistors must be enabled to avoid floating

inputs.

–

Port P6

PP6 must be configured as output or its pull resistor must be enabled to avoid a floating input.

–

Port S[3:2]

PS3:2 must be configured as outputs or their pull resistors must be enabled to avoid floating

inputs.

–

PAD[15:8] (ATD1 channels)

OutofresettheATD1isdisabledpreventingcurrentflowsinthepins.DonotmodifytheATD1

registers!

Document References

The Device User Guide provides information about the MC9S12DT128 device made up of standard

HCS12 blocks and the HCS12 processor core.

This document is part of the customer documentation. A complete set of device manuals also includes all

theindividualBlockUserGuidesoftheimplementedmodules.Inaefforttoreduceredundancyallmodule

specific information is located only in the respective Block User Guide. If applicable, special

implementation details of the module are given in the block description sections of this document.

See

Table 0-2

for names and versions of the referenced documents throughout the Device User Guide.

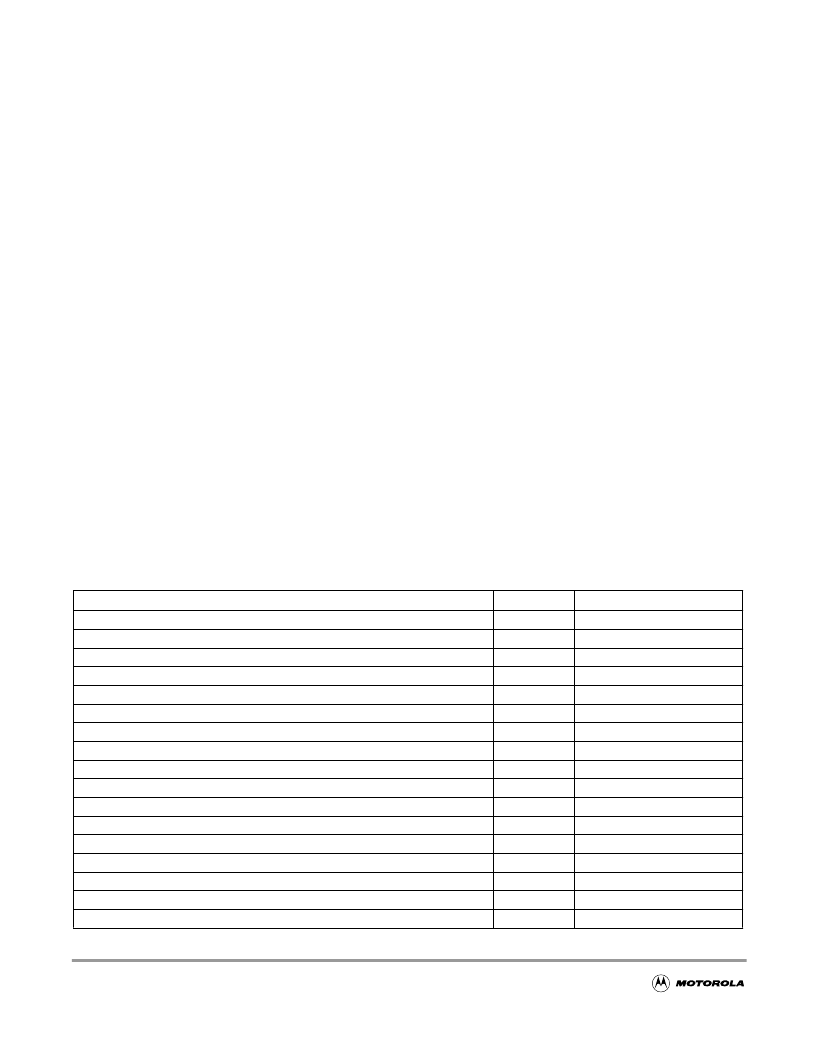

Table 0-2 Document References

User Guide

HCS12 CPU Reference Manual

HCS12 Module Mapping Control (MMC) Block Guide

HCS12 Multiplexed External Bus Interface (MEBI) Block Guide

HCS12 Interrupt (INT) Block Guide

HCS12 Background Debug Module (BDM) Block Guide

HCS12 Breakpoint (BKP) Block Guide

Clock and Reset Generator (CRG) Block User Guide

Oscillator (OSC) Block User Guide

Enhanced Capture Timer 16 Bit 8 Channel (ECT_16B8C) Block User Guide

Analog to Digital Converter 10 Bit 8 Channel (ATD_10B8C) Block User Guide

Inter IC Bus (IIC) Block User Guide

Asynchronous Serial Interface (SCI) Block User Guide

Serial Peripheral Interface (SPI) Block User Guide

Pulse Width Modulator 8 Bit 8 Channel (PWM_8B8C) Block User Guide

128K Byte Flash (FTS128K) Block User Guide

2K Byte EEPROM (EETS2K) Block User Guide

Byte Level Data Link Controller -J1850 (BDLC) Block User Guide

Version

V02

V04

V03

V01

V04

V01

V04

V02

V01

V02

V02

V02

V02

V01

V02

V01

V01

Document Order Number

S12CPUV2/D

S12MMCV4/D

S12MEBIV3/D

S12INTV1/D

S12BDMV4/D

S12BKPV1/D

S12CRGV4/D

S12OSCV2/D

S12ECT16B8CV1/D

S12ATD10B8CV2/D

S12IICV2/D

S12SCIV2/D

S12SPIV2/D

S12PWM8B8CV1/D

S12FTS128KV2/D

S12EETS2KV1/D

S12BDLCV1/D

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S12DTB128PIMV2D | MC9S12DT128 Device User Guide V02.09 |

| S12ECT16B8CV1 | MC9S12DT128 Device User Guide V02.09 |

| S12ECT16B8CV1D | MC9S12DT128 Device User Guide V02.09 |

| S12EETS2KV1 | MC9S12DT128 Device User Guide V02.09 |

| S12EETS2KV1D | MC9S12DT128 Device User Guide V02.09 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S12DTB128PIMV2D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| S12EB7C-B | 制造商:HB 制造商全稱:HB Electronic Components 功能描述:LED |

| S12ECT16B8CV1 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| S12ECT16B8CV1D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| S12EETS1KV1D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MC9S12DJ64 Device User GUide V01.17 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。