- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365955 > S80C186EC13 MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | S80C186EC13 |

| 英文描述: | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| 中文描述: | 微處理器| 16位|的CMOS | QFP封裝| 100引腳|塑料 |

| 文件頁數(shù): | 56/57頁 |

| 文件大小: | 585K |

| 代理商: | S80C186EC13 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當前第56頁第57頁

80C186EC/188EC, 80L186EC/188EC

INSTRUCTION SET SUMMARY

(Continued)

80C186EC

Clock

Cycles

80C188EC

Clock

Cycles

Function

Format

Comments

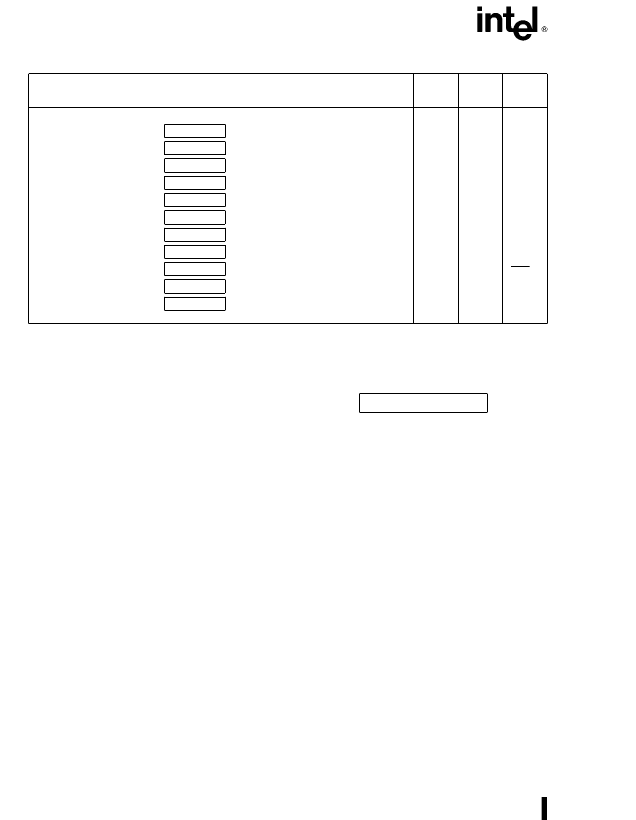

PROCESSOR CONTROL

CLC

e

Clear carry

1 1 1 1 1 0 0 0

2

2

CMC

e

Complement carry

1 1 1 1 0 1 0 1

2

2

STC

e

Set carry

1 1 1 1 1 0 0 1

2

2

CLD

e

Clear direction

1 1 1 1 1 1 0 0

2

2

STD

e

Set direction

1 1 1 1 1 1 0 1

2

2

CLI

e

Clear interrupt

1 1 1 1 1 0 1 0

2

2

STI

e

Set interrupt

1 1 1 1 1 0 1 1

2

2

HLT

e

Halt

1 1 1 1 0 1 0 0

2

2

WAIT

e

Wait

1 0 0 1 1 0 1 1

6

6

if TEST

e

0

LOCK

e

Bus lock prefix

1 1 1 1 0 0 0 0

2

2

NOP

e

No Operation

1 0 0 1 0 0 0 0

3

3

(TTT LLL are opcode to processor extension)

Shaded areas indicate instructions not available in 8086/8088 microsystems.

NOTE:

*

Clock cycles shown for byte transfers, for word operations, add 4 clock cycles for all memory transfers.

The Effective Address (EA) of the memory operand

is computed according to the mod and r/m fields:

if mod

e

11 then r/m is treated as a REG field

if mod

e

00 then DISP

e

0

*

, disp-low and disp-

high are absent

if mod

e

01 then DISP

e

disp-low sign-extended

to 16-bits, disp-high is absent

if mod

e

10 then DISP

e

disp-high: disp-low

if r/m

e

000 then EA

e

(BX)

a

(SI)

a

DISP

if r/m

e

001 then EA

e

(BX)

a

(DI)

a

DISP

if r/m

e

010 then EA

e

(BP)

a

(SI)

a

DISP

if r/m

e

011 then EA

e

(BP)

a

(DI)

a

DISP

if r/m

e

100 then EA

e

(SI)

a

DISP

if r/m

e

101 then EA

e

(DI)

a

DISP

if r/m

e

110 then EA

e

(BP)

a

DISP

*

if r/m

e

111 then EA

e

(BX)

a

DISP

DISP follows 2nd byte of instruction (before data if

required)

*

except if mod

e

00 and r/m

e

110 then EA

e

disp-high: disp-low.

EA calculation time is 4 clock cycles for all modes,

and is included in the execution times given whenev-

er appropriate.

Segment Override Prefix

0

0

1

reg

1

1

0

reg is assigned according to the following:

Segment

Register

ES

CS

SS

DS

reg

00

01

10

11

REG is assigned according to the following table:

16-Bit (w

e

1)

000 AX

001 CX

010 DX

011 BX

100 SP

101 BP

110 SI

111 DI

8-Bit (w

e

0)

000 AL

001 CL

010 DL

011 BL

100 AH

101 CH

110 DH

111 BH

The physical addresses of all operands addressed

by the BP register are computed using the SS seg-

ment register. The physical addresses of the desti-

nation operands of the string primitive operations

(those addressed by the DI register) are computed

using the ES segment, which may not be overridden.

56

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S80C186EC-13 | 16-Bit Microprocessor |

| S80C186EC25 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| S80C186EC-25 | 16-Bit Microprocessor |

| S80C188EC13 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| S80C188EC25 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S80C186EC-13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| S80C186EC16 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| S80C186EC20 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| S80C186EC25 | 功能描述:IC MPU 16-BIT 5V 25MHZ 100-MQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| S80C186EC-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。