- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25623 > S80C32E-40SHXXX:RD (TEMIC SEMICONDUCTORS) 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | S80C32E-40SHXXX:RD |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 |

| 文件頁(yè)數(shù): | 91/109頁(yè) |

| 文件大小: | 10824K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)當(dāng)前第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)

68

ATtiny20 [DATASHEET]

8235E–AVR–03/2013

TOP the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the

opposite logic values.

At the very start of period 2 in Figure 11-7 on page 67 OCnx has a transition from high to low even though there is no

Compare Match. The point of this transition is to guaratee symmetry around BOTTOM. There are two cases that give a

transition without Compare Match.

OCR0x changes its value from TOP, like in Figure 11-7 on page 67. When the OCR0x value is TOP the OCnx pin

value is the same as the result of a down-counting Compare Match. To ensure symmetry around BOTTOM the

OCnx value at TOP must correspond to the result of an up-counting Compare Match.

The timer starts counting from a value higher than the one in OCR0x, and for that reason misses the Compare

Match and hence the OCnx change that would have happened on the way up.

11.8

Timer/Counter Timing Diagrams

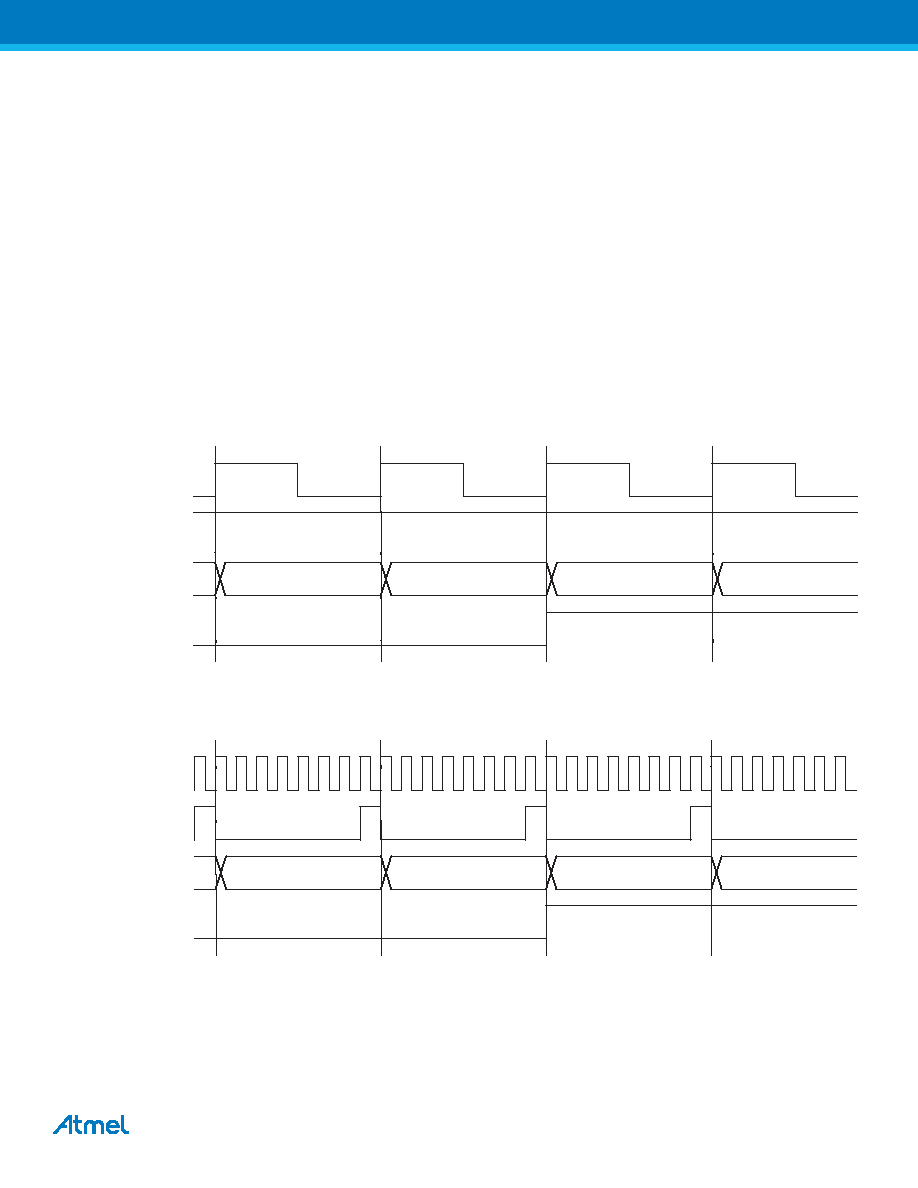

The Timer/Counter is a synchronous design and the timer clock (clkT0) is therefore shown as a clock enable signal in the

following figures. The figures include information on when Interrupt Flags are set. Figure 11-8 on page 68 contains timing

data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other

than phase correct PWM mode.

Figure 11-8. Timer/Counter Timing Diagram, no Prescaling

Figure 11-9 on page 68 shows the same timing data, but with the prescaler enabled.

Figure 11-9. Timer/Counter Timing Diagram, with Prescaler (f

clk_I/O/8)

Figure 11-10 on page 69 shows the setting of OCF0B in all modes and OCF0A in all modes except CTC mode and PWM

mode, where OCR0A is TOP.

clk

Tn

(clk

I/O/1)

TOVn

clk

I/O

TCNTn

MAX - 1

MAX

BOTTOM

BOTTOM + 1

TOVn

TCNTn

MAX - 1

MAX

BOTTOM

BOTTOM + 1

clk

I/O

clk

Tn

(clk

I/O/8)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S80C52TXXX-12 | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| S80C31-20D | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| S80C154-20R | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| S83C154CXXX-36R | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQCC44 |

| S80C52TXXX-12 | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S80C32-L16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| S80C32-L16R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| S80C376CB8 WAF | 制造商:Intel 功能描述: |

| S80C42 | 制造商:Intel 功能描述: |

| S80C51 WAF | 制造商:Intel 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。