- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372096 > S83C751-5A28 (NXP SEMICONDUCTORS) 8-bit Microcontroller with 2/4/8K Bytes In-System Programmable Flash PDF資料下載

參數(shù)資料

| 型號: | S83C751-5A28 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-bit Microcontroller with 2/4/8K Bytes In-System Programmable Flash |

| 中文描述: | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQCC28 |

| 封裝: | PLASTIC, MO-047AB, SOT-261-3, LCC-28 |

| 文件頁數(shù): | 16/24頁 |

| 文件大?。?/td> | 211K |

| 代理商: | S83C751-5A28 |

Philips Semiconductors

Product specification

83C751/87C751

80C51 8-bit microcontroller family

2K/64 OTP/ROM, I

2

C, low pin count

1998 May 01

16

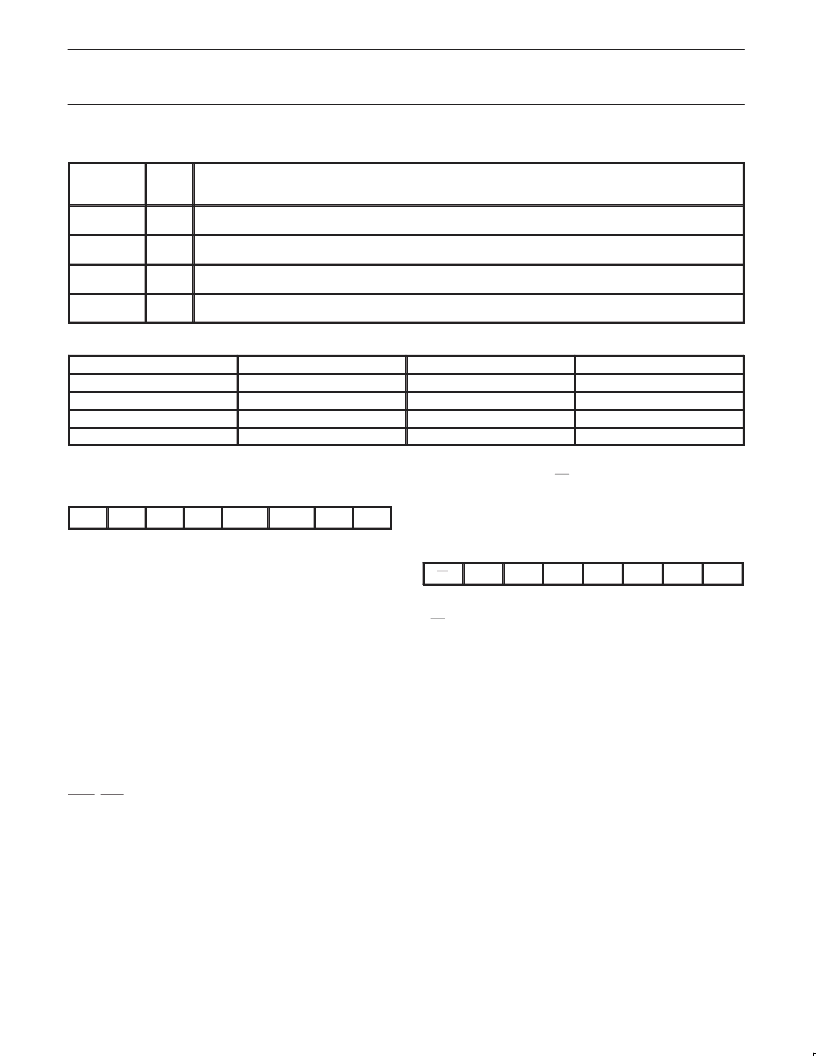

Table 4.

Interaction of TIRUN with SLAVEN, MASTRQ, and MASTER

SLAVEN,

MASTRQ,

MASTER

TIRUN

OPERATING MODE

All 0

0

The I

2

C interface is disabled. Timer I is cleared and does not run. This is the state assumed after a reset. If an I

2

C

application wants to ignore the I

2

C at certain times, it should write SLAVEN, MASTRQ, and TIRUN all to zero.

The I

2

C interface is disabled. Timer I operates as a free-running time base. Use this mode only in non-I

2

C

applications.

The I

2

C interface is enabled. The 3 low-order bits of Timer I run for min-time generation, but the hi-order bits do

not, so that there is no checking for I

2

C being “hung.” This configuration can be used for very slow I

2

C operation.

The I

2

C interface is enabled. Timer I runs during frames on the I

2

C, and is cleared by transitions on SCL, and by

Start and Stop conditions. This is the normal state for I

2

C operation.

All 0

1

Any or all 1

0

Any or all 1

1

Table 5.

CT1, CT0 Values

CT1, CT0

OSC/12 COUNT

f

OSC

MAX

16.8MHz

TIMEOUT PERIOD

10

7

1023 cycles

01

6

14.4MHz

1022 cycles

00

5

12.0MHz

1021 cycles

11

4

9.6MHz

1020 cycles

I

2

C Register I2STA

READ ONLY

7

6

5

4

3

2

1

0

–

IDLE

XDATA

XACTV

MAKSTR

MAKSTP

XSTR

XSTP

MSB

LSB

This register is read only and reflects the internal status of the I

2

C

hardware. IDLE, XSTR, and XSTP reflect the status of the like

named bits in the I2CON register.

XDATA

XACTV

MAKSTR This bit is high while the hardware is effecting a start

condition.

MAKSTP This bit is high while the hardware is effecting a stop

condition.

XSTR

This bit is active while the hardware is effecting a

repeated start condition.

XSTP

This bit is active while the hardware is effecting a

repeated stop condition.

The content of the transmitter buffer.

Transmitter active.

Interrupts

The interrupt structure is a five-source, one-level interrupt system.

Interrupt sources common to the 80C51 are the external interrupts

(INT0, INT1) and the timer/counter interrupt (ET0). The I

2

C interrupt

(EI2) and Timer I interrupt (ETI) are the other two interrupt sources.

The interrupt sources are listed below in their order of polling

sequence priority.

Upon interrupt or reset the program counter is loaded with specific

values for the appropriate interrupt service routine in program

memory. These values are:

Program Memory

Address

000

003

00B

013

01B

023

Event

Reset

INT0

Counter/Timer 0

INT1

Timer I

I

2

C

Priority

Highest

Lowest

The interrupt enable register (IE) is used to individually enable or

disable the five sources. Bit EA in the interrupt enable register can

be used to globally enable or disable all interrupt sources. The

interrupt enable register is described below. All other interrupt details

are based on the 80C51 interrupt architecture.

Interrupt Enable Register

7

6

5

4

3

2

1

0

EA

X

X

EI2

ETI

EX1

ET0

EX0

Symbol Position

Function

EA

IE.7

Disables all interrupts. If EA = 0, no interrupt

will be acknowledged. If EA = 1, each interrupt

source is individually enabled or disabled by

setting or clearing its enable bit

–

IE.6

Reserved

–

IE.5

Reserved

EI2

IE.4

Enables or disables the I

2

C interrupt.

If EI2 = 0, the I

2

C interrupt is disabled

ETI

IE.3

Enables or disables the Timer I overflow

interrupt. If ETI = 0, the Timer I interrupt is

disabled.

EX1

IE.2

Enables or disables external interrupt 1.

If EX1 = 0, external interrupt 1 is disabled.

ET0

IE.1

Enables or disables the Timer 0 overflow

interrupt. If ET0 = 0, theTimer 0 interrupt is

disabled.

EX0

IE.0

Enables or disables external interrupt 0.

If EX0 = 0, external interrupt 0 is disabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S83C751-5N24 | 8-bit Microcontroller with 2/4/8K Bytes In-System Programmable Flash |

| S83C752-5N28 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S87C752-6A28 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S87C752-6N28 | CONN JACK PHONE MINI .101 2POS |

| S83C752-6A28 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S83C751-5N24 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 2K/64 OTP/ROM, I2C, low pin count |

| S83C752-1A28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S83C752-1DB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S83C752-1N28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S83C752-2A28 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。