- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373361 > SA25C512LEMN (Electronic Theatre Controls, Inc.) DUCT CORNER STRIP PVC LTGY 2H PDF資料下載

參數(shù)資料

| 型號(hào): | SA25C512LEMN |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | DUCT CORNER STRIP PVC LTGY 2H |

| 中文描述: | 512KB的EEPROM中具有10MHz的SPI和低待機(jī) |

| 文件頁數(shù): | 11/19頁 |

| 文件大小: | 1078K |

| 代理商: | SA25C512LEMN |

SA25C512 Data Sheet

SAIFUN

11

Read Status Register (RDSR)

The RDSR instruction provides read

access to the status register. The

BUSY/RDY and WREN statuses of the

device can also be determined by this

instruction. In addition, the Block Write

Protection bits indicate the extent of

protection employed. In order to determine

the status of the device, the value of the

/RDY bit can be continuously polled before

sending any write instruction.

Write Status Register (WRSR)

The WRSR instruction enables the user to

select one of four levels of protection. The

SA25C512 is divided into four array

segments. The top quarter, top half or all of

the memory segments can be protected

(for more details, refer to Table 7). The

data within a selected segment is therefore

read-only.

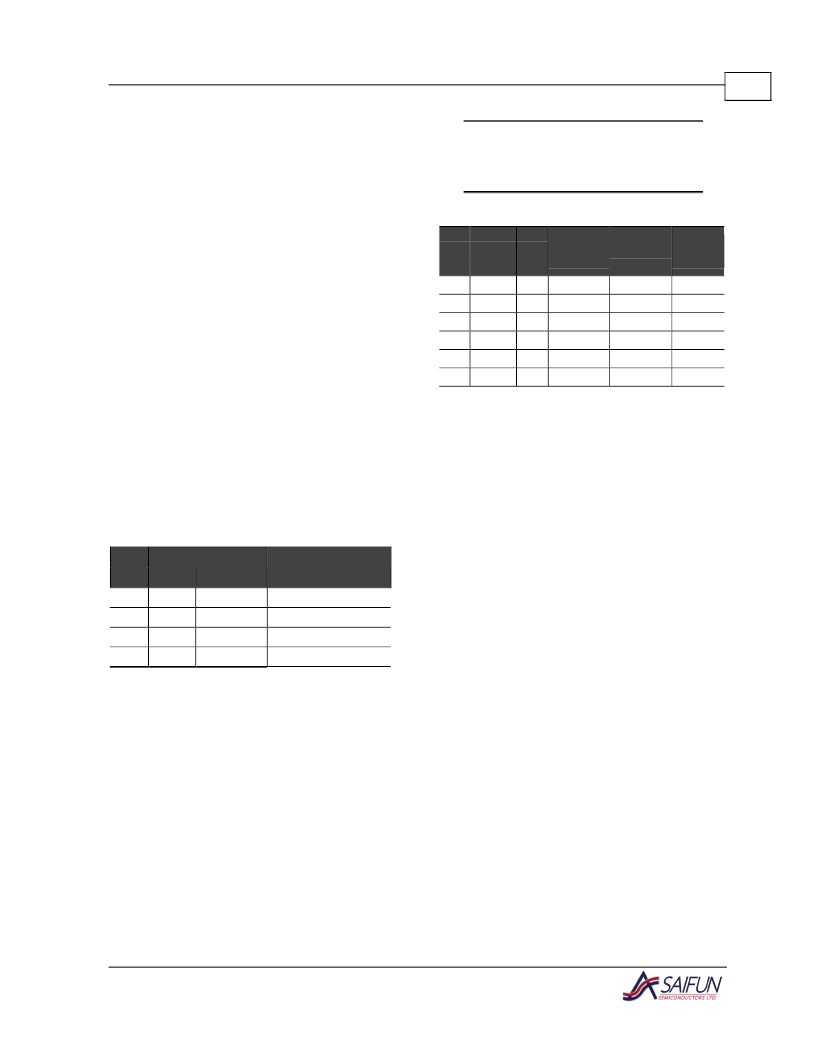

Table 7. Block Write Protect Bits

Status Register Bits

Level

BP1

BP0

Array Addresses

Protected

0

0

0

None

1/4

0

1

C000 - FFFF

1/2

1

0

8000 - FFFF

All

1

1

0000 - FFFF

The WRSR instruction (as shown in

Table 8) also allows the user to enable or

disable the WPb pin via the WPBEN bit.

Hardware write protection is enabled when

the WPb pin is low and the WPBEN bit is

1, and disabled when either the WP pin is

high or the WPBEN bit is 0. When the

device is hardware write protected, writes

to the status register are disabled.

NOTE:

When the WPBEN bit is hardware write

protected, it cannot be changed back

to 0 as long as the WPb pin is held low.

Table 8. WPBEN Operation

WPb WPBEN WENPBlocks

Un-

protected

Blocks

Status

Register

X

0

0

Protected

Protected Protected

X

0

1

Protected

Writable

Writable

Low

1

0

Protected

Protected Protected

Low

1

1

Protected

Writable

Protected

High

X

0

Protected

Protected Protected

High

X

1

Protected

Writable

Writable

Read Sequence (READ)

Reading the SA25C512 via the SO pin

requires the following sequence (for more

details, see Table 9, page 12):

1. After the CSb line is pulled low to select

the device, the READ opcode is

transmitted via the SI line, followed by

the byte address to be read. Upon

completion, any data on the SI line is

ignored.

2. The data (D7-D0) at the specified

address is then shifted out onto the SO

line.

If only one byte is to be read, the CSb line

should be driven high after the data comes

out.

The

READ

continued,

as

the

automatically

incremented

continues to shift out. When the highest

address is reached, the address counter

rolls over to the lowest address, enabling

the entire memory to be read in one

continuous READ cycle.

sequence

byte

can

be

is

address

and

data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SA25C512LEN | DUCT CORNER STRIP PVC LT GY 3H |

| SA25C512LMN | DUCT CORNER STRIP PVC LT GY 4H |

| SA25C512LN | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SA25C512HEMNX | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SA25C512HEN | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SA25C512LEMNX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Kb EEPROM SPI with 10MHz and Low Standby |

| SA25C512LEN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Kb EEPROM SPI with 10MHz and Low Standby |

| SA25C512LENX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Kb EEPROM SPI with 10MHz and Low Standby |

| SA25C512LMN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Kb EEPROM SPI with 10MHz and Low Standby |

| SA25C512LMNX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Kb EEPROM SPI with 10MHz and Low Standby |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。