- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372108 > SA8027DH (NXP SEMICONDUCTORS) 2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer PDF資料下載

參數(shù)資料

| 型號(hào): | SA8027DH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | XO, clock |

| 英文描述: | 2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 |

| 封裝: | PLASTIC, TSSOP-20 |

| 文件頁(yè)數(shù): | 12/22頁(yè) |

| 文件大?。?/td> | 231K |

| 代理商: | SA8027DH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

Philips Semiconductors

Product data

SA8027

2.5 GHz low voltage, low power

RF fractional-N/IF integer frequency synthesizer

2001 Aug 21

12

2.0

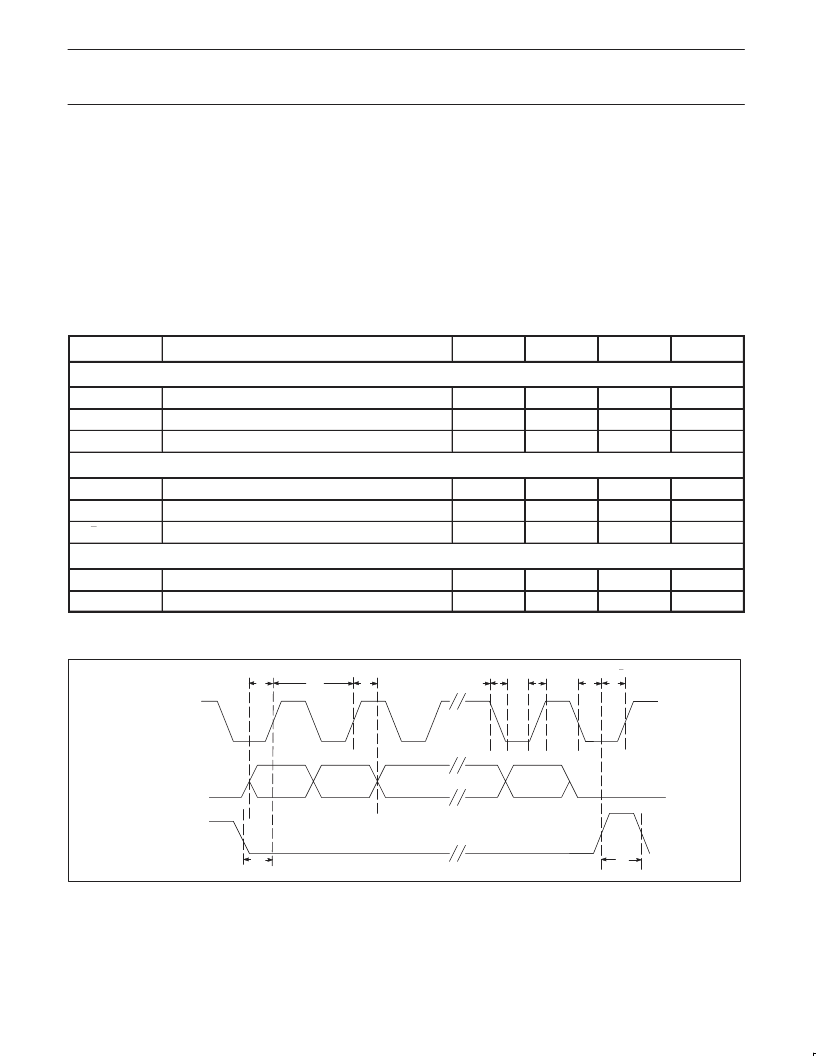

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to

program all counter divide ratios, fractional compensation DAC,

selection and enable bits. The programming data is structured into

24 bit words; each word includes 2 or 3 address bits. Figure 11

shows the timing diagram of the serial input. When the STROBE

goes active HIGH, the clock is disabled and the data in the shift

register remains unchanged. Depending on the address bits, the

data is latched into the selected working registers or temporary

registers. In order to fully program the synthesizer, 3 words must be

SERIAL PROGRAMMING BUS

sent: C, B, and A, in that order. A typical programming sequence is

illustrated in Figure 12. Table 2 shows the format and the contents of

each word. The D word is used for testing purposes and should be

initially set to 0 for normal operation. When sending the B-word, data

bits FC7–0 for the fractional compensation DAC are not loaded

immediately. Instead they are stored in temporary registers. Only

when the A-word is loaded, these temporary registers are loaded

together with the main divider ratio.

2.1

V

DD

= V

DDCP

=+3.0 V; T

amb

= +25

°

C unless otherwise specified.

Serial bus timing characteristics

(see Figure 11)

SYMBOL

PARAMETER

MIN.

TYP.

MAX.

UNIT

Serial programming clock; CLK

t

r

Input rise time

–

10

40

ns

t

f

Input fall time

–

10

40

ns

T

cy

Clock period

100

–

–

ns

Enable programming; STROBE

t

START

Delay to rising clock edge

40

–

–

ns

t

W

Minimum inactive pulse width

1/f

COMP

–

–

ns

t

SU;E

Enable set-up time to next clock edge

20

–

–

ns

Register serial input data; DATA

t

SU;DAT

Input data to clock set-up time

20

–

–

ns

t

HD;DAT

Input data to clock hold time

20

–

–

ns

Application information

SR01417

CLK

DATA

STROBE

LSB

ADDRESS

t

SU;DAT

t

HD;DAT

t

f

t

w

t

r

t

SU;E

t

START

T

cy

MSB

≥

0

Figure 11.

Serial Bus Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SA8027W | 2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer |

| SA8028 | 2.5 GHz sigma delta fractional-N / 760 MHz IF integer frequency synthesizers |

| SA8028W | ECONOLINE: RB & RA - Dual Output from a Single Input Rail- Power Sharing on Output- Industry Standard Pinout- 1kVDC & 2kVDC Isolation- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 85% |

| SA90-0001 | Vector Modulator, 1.94 to 2.24 GHz |

| SA90-0001-DC000 | Dual Linear Driver for Vector Modulators |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SA8027DH,512 | 功能描述:射頻無(wú)線雜項(xiàng) DUAL FRACTIONAL N RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| SA8027DH,518 | 功能描述:鎖相環(huán) - PLL DUAL FRACTIONAL N RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| SA8027DH-T | 功能描述:鎖相環(huán) - PLL DUAL FRACTIONAL N SYNTHESIZER RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| SA8027W | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer |

| SA8028 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.5 GHz sigma delta fractional-N / 760 MHz IF integer frequency synthesizers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。