- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372109 > SAA4700 (NXP SEMICONDUCTORS) VPS dataline processor PDF資料下載

參數(shù)資料

| 型號: | SAA4700 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | VPS dataline processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDIP18 |

| 封裝: | 0.300 INCH, PLASTIC, DIP-18 |

| 文件頁數(shù): | 4/12頁 |

| 文件大?。?/td> | 65K |

| 代理商: | SAA4700 |

March 1991

4

Philips Semiconductors

Preliminary specification

VPS dataline processor

SAA4700

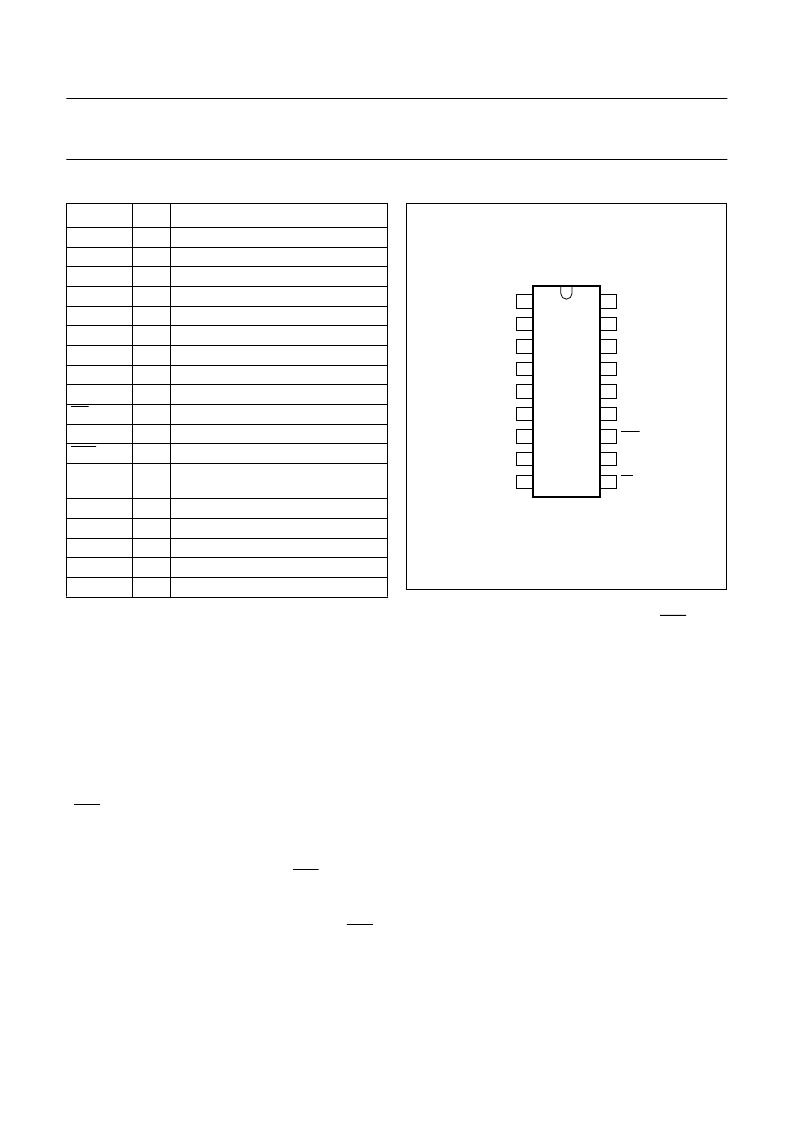

PINNING

SYMBOL

PIN

DESCRIPTION

CVBS

SYNC

GND1

GND2

C

black

CSO

AD

SCL

SDA

RS

TP

DAV

1

2

3

4

5

6

7

8

9

10

11

12

video signal input (CVBS from TV)

sync amplitude input (CVBS from TV)

analog ground (0 V)

digital ground (0 V)

capacitor for black level

composite sync output

address set input

I

2

C-bus clock line

I

2

C-bus data line

reset input active LOW

test point for line 16 decoder

data available output active LOW

oscillator resistor for frequency

adjustment

test point clock pulse

+

5 V supply voltage (digital part)

+

5 V supply voltage (analog part)

capacitor of phase detector

not connected

R

osc

13

CP

V

P1

V

P2

C

ph

n.c.

14

15

16

17

18

PIN CONFIGURATION

Fig.2 Pin configuration

handbook, halfpage

SAA4700

MBH796

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

CVBS

SYNC

GND1

GND2

CSO

AD

SCL

SDA

Cblack

n.c.

RS

TP

DAV

CP

Rosc

VP1

VP2

Cph

External reset

The circuit provides an internal

power-on reset. When using this

facility pin 10 should be connected to

V

P

or, if external reset

(RESET = LOW) is to be used pin 10

should be prepared by connecting pin

10 via a 10 k

pull-up resistor to V

P

.

Reset forces the following:

- I

2

C-bus not to acknowledge

- DAV output to go HIGH (pin 12)

- I

2

C-bus transfer register to “FFF”

CVBS input

The CVBS signal is applied to the

sync separator (pin 2) via a

decoupling capacitor and to the data

slicer (pin 1) via an RC high-pass

filter.

To enable proper storage of the sync

value in the decoupling capacitor, the

sync generator output resistance

should not exceed 1 k

.

Black level

The capacitor connected to pin 5

stores the black level value for the

adaptive sync slicer.

Composite sync output (CSO)

A composite sync output signal for

customer application is provided

(pin 6).

DAV output

The data available output pin 12 is set

LOW after an error free dataline 16 is

received. DAV returnes to HIGH after

the beginning of the next first field. If

no valid data is available DAV

remains HIGH. A short duration pulse

of 1

μ

s (Fig.5) is inserted at the

beginning of dataline 16; it will ensure

that a HIGH-to-LOW transmission

occurs which can then be used for

triggering.

5 MHz VCO and phase detector

The resistor connected between pin

13 and V

P2

determines the current

into the voltage controlled oscillator.

The RC network connected to pin 17

acts as a low-pass filter for the phase

detector.

Power supply

To prevent crosscoupling the circuit is

provided with separate ground and

supply pins for analog and digital

parts (pins 3, 4, 15 and 16).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA4945H | LIne MEmory noise Reduction IC LIMERIC |

| SAA4951 | RES 6.49K OHM 1/16W 0.5% 0402SMD |

| SAA4951WP | Memory controller |

| SAA4952WP | Memory controller |

| SAA4955 | 2.9-Mbit field memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA4700T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:VPS dataline processor |

| SAA4945H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LIne MEmory noise Reduction IC LIMERIC |

| SAA4951 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Memory controller |

| SAA4951WP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Memory controller |

| SAA4952WP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Memory controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。