- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372109 > SAA5249 (NXP Semiconductors N.V.) Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX PDF資料下載

參數(shù)資料

| 型號(hào): | SAA5249 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| 中文描述: | 綜合貴賓和圖文電視的背景內(nèi)存控制器IVT1.1BMCX |

| 文件頁數(shù): | 25/44頁 |

| 文件大?。?/td> | 821K |

| 代理商: | SAA5249 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

1996 Nov 07

25

Philips Semiconductors

Preliminary specification

Integrated VIP and Teletext with

Background Memory Controller

SAA5249

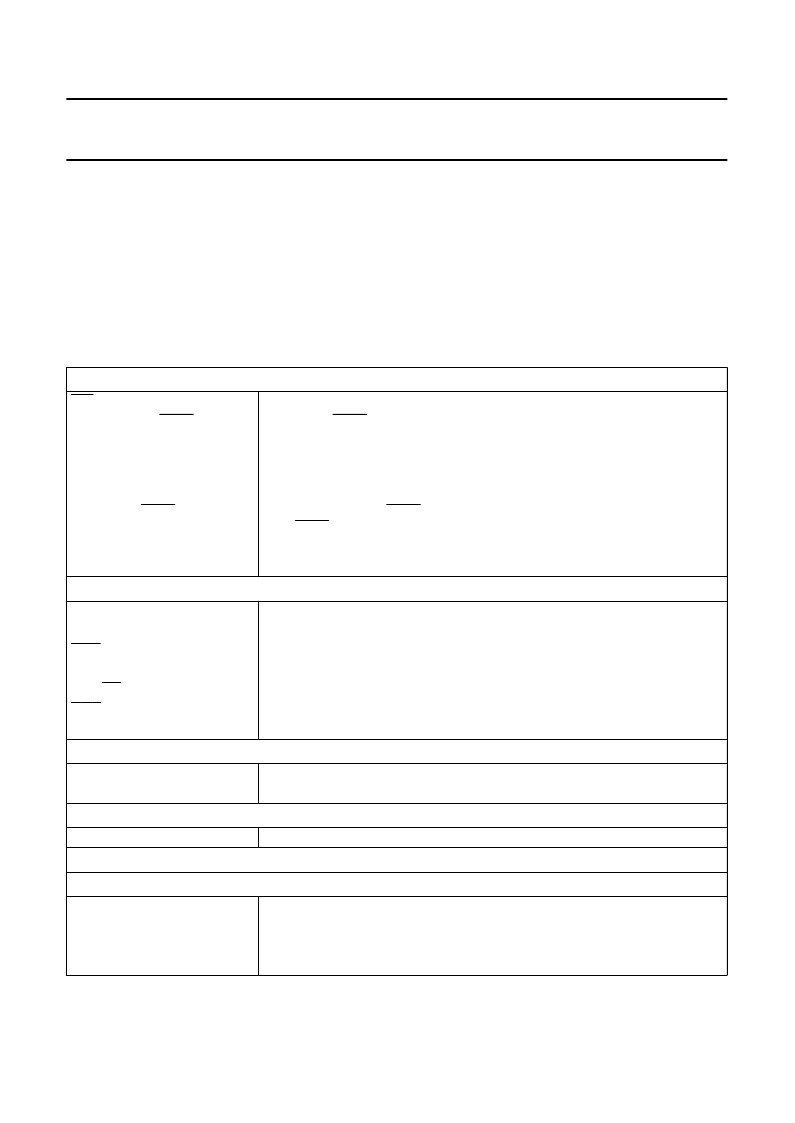

Notes

1.

2.

The dash (

) indicates these bits are inactive and must be written to logic 0 for future compatibility.

All bits in registers R0 to R10 are cleared to logic 0 on power-up except bits D0 and D1 of Registers R1, R5 and R6

which are set to logic 1.

All memory is cleared to space (00100000) on power-up, except Row 0 Column 7 Chapter 0, which is alpha white

(00000111) as the acquisition circuit is enabled but the page is on hold.

TB must be set to logic 0 for normal operation.

The I

2

C-bus slave address is 0010001.

3.

4.

5.

Table 8

Register description

R0 ADVANCED CONTROL - auto increments to register 1

R11/R11B SELECT

DISABLE ODD/EVEN

DISPLAY STATUS ROW

selects reading of R11 or R11B

forces ODD/EVEN output LOW when logic 1

when SET = 1 and R1D6 = 1 open (8-bit mode) then all the text display is blanked

out apart from the status row, this allows the page memory to be used for

non-textural data, such as in the German TOP system

disables green rolling header and time

when set forces ODD/EVEN LOW if any TV picture displayed, if DISABLE

ODD/EVEN = 0

will force the PLL to free run in all conditions

automatic display of FASTEXT prompt row when logic 1

DISABLE HDR ROLL

AUTO ODD/EVEN

FREE RUN PLL

X24 POS

R1 MODE - auto increments to register 2

T0, T1

TCS ON

DEW/FULL FIELD

DISABLE PKT 26

ACQ ON/OFF

7 + P/8-BIT

VCS TO SCS

interlace/non-interlace 312/313 line control (see Table 10)

text composite sync or direct sync select (see Table 10 for FFB mode selection)

field-flyback or full-channel mode

disable automatic processing of packet 26

acquisition circuits turned off when logic 1

7-bits with parity checking or 8-bit mode

when logic 1 enables display of messages with 60 Hz input signal

R2 PAGE REQUEST ADDRESS - auto increments to register 3

COL SCO - SC2

TB

point to start column for page request data (see Table 9)

must be logic 0 for normal operation

R3 PAGE REQUEST DATA - does not auto increment

(see Table 9)

CLEAR B.M.

when set to logic 1. Useful when transmission channel changes

R5 NORMAL DISPLAY CONTROL - auto increments to register 6

R6 NEWSFLASH/SUBTITLE DISPLAY CONTROL - auto increments to register 7;

(note 1)

PON

TEXT

COR

BKGND

picture on

text on

contrast reduction on

background colour on

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA5249P | Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| SAA5250 | Interface for data acquisition and control for multi-standard teletext systems |

| SAA5250P | Interface for data acquisition and control for multi-standard teletext systems |

| SAA5250T | Interface for data acquisition and control for multi-standard teletext systems |

| SAA5252 | Line twenty-one acquisition and display LITOD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA5249GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| SAA5249GP/E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| SAA5249P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| SAA5249P/E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated VIP and Teletext with Background Memory Controller IVT1.1BMCX |

| SAA5250 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Interface for data acquisition and control for multi-standard teletext systems |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。