- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372127 > SC68C562C1 (NXP Semiconductors N.V.) CMOS dual universal serial communications controller CDUSCC PDF資料下載

參數(shù)資料

| 型號: | SC68C562C1 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CMOS dual universal serial communications controller CDUSCC |

| 中文描述: | CMOS雙通用串行通信控制器CDUSCC |

| 文件頁數(shù): | 8/26頁 |

| 文件大小: | 163K |

| 代理商: | SC68C562C1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

Philips Semiconductors

Product specification

SC68C562

CMOS Dual universal serial communications controller

(CDUSCC)

1998 Sep 04

8

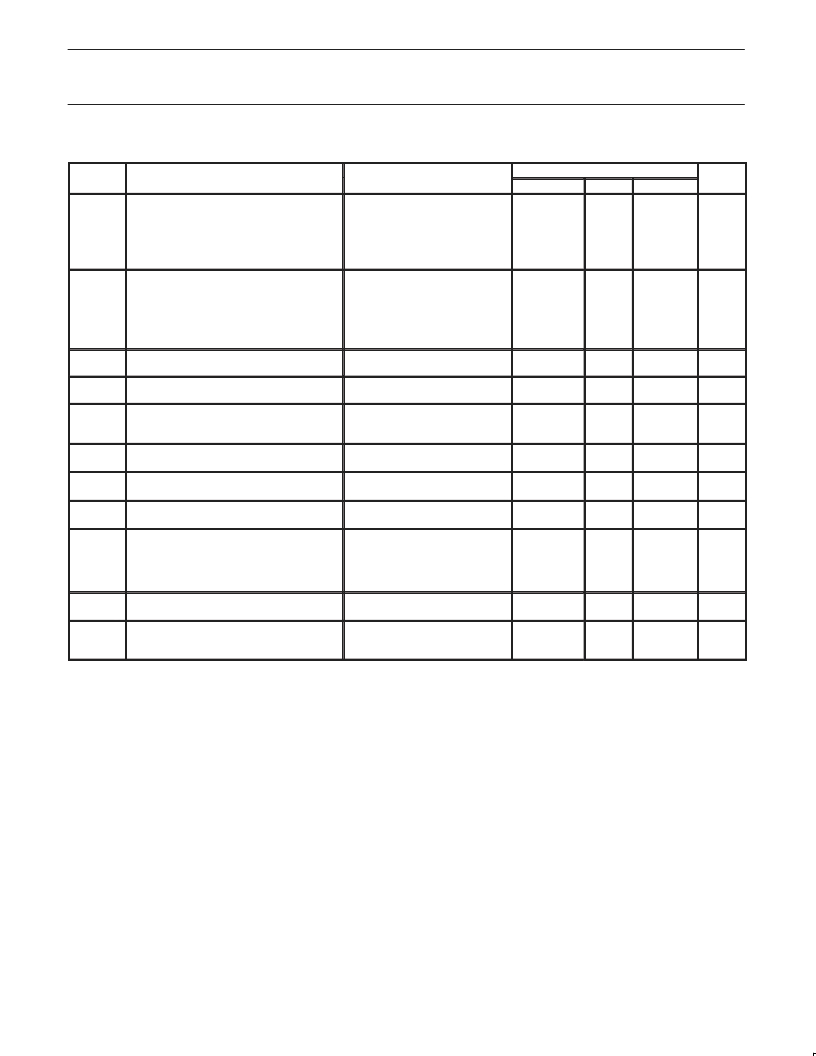

DC ELECTRICAL CHARACTERISTICS

4, 5

T

A

= 0 to +70

°

C, –40 to +85 C, V

CC

= 5.0V

10%

SYMBOL

PARAMETER

TEST CONDITIONS

LIMITS

Typ

UNIT

Min

Max

V

IL

V

IH

Input low voltage:

All except X1/CLK

X1/CLK

Input high voltage:

All except X1/CLK

X1/CLK

0 to 70 C

–40 to 85 C

2.0

2.3

0.8xV

CC

0.8

0.8

V

CC

V

V

V

V

V

V

OL

V

OH

Output low voltage:

14

All except IRQN

IRQN

7

Output high voltage:

14

(Except open drain outputs)

I

OL

= 5.3mA (Comm), 4.8mA

(Indus)

I

OL

= 8.8mA (Comm), 7.8mA

(Indus)

I

OH

= -400

μ

A

V

IN

= 0, X2 = GND

V

IN

= V

CC

, X2 = GND

X1 open V

IN

= 0

V

IN

= V

CC

V

CC

–0.5

0.5

0.5

V

V

V

I

ILX1

I

IHX1

I

SCX2

X1/CLK input low current

10

X1/CLK input high current

10

X2 short circuit current (X2 mode)

–150

0.0

150

–15

+15

μ

A

μ

A

mA

mA

I

IL

Input low current

RESETN, DTCN, TxDAKA/BN,

RTxDAKA/BN

Input leakage current

V

IN

= 0

-15

–0.5

μ

A

I

L

V

IN

= 0 to V

CC,

0 to 70 C

–40 to 85 C

V

IN

= V

0 to 70 C

–40 to 85 C

V

IN

= 0

,

0 to 70 C

–40 to 85 C

V

IN

= 0

V

IN

= V

CC

-1

–10

+1

+10

+1

+10

μ

A

I

OZH

Output off current high, 3-State data bus

μ

A

μ

A

μ

A

μ

A

I

OZL

Output off current low, 3-State data bus

-1

–10

I

ODL

I

ODH6

Open drain output low current in off

state:

DONEN

,

DTACKN (3-state)

IRQN

Open drain output high current in off

state:

DONEN, IRQN, DTACKN (3-state)

Power supply current

16

(See Figure 17 for graphs)

Input capacitance

9

Output capacitance

9

Input/output capacitance

9

-1

5

-1

–1

-0.5

+1

80

95

10

15

20

μ

A

μ

A

μ

A

mA

I

CC

0 to 70 C

–40 to 85 C

V

CC

= GND = 0

V

CC

= GND = 0

V

CC

= GND = 0

25

C

IN

C

OUT

C

I/O

NOTES:

1. Stresses above those listed under Abs. Max Ratings may cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied.

2. Clock may be stopped (DC) for testing purposes or when the CDUSCC is in non-operational modes. Operation down to 0 rate clocks is

implied by a full static CMOS design, but is not verified in testing or characterization.

3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static

charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

4. Parameters are valid over specified temperature and voltage range.

5. All voltage measurements are referenced to ground (GND). For testing, all inputs except X1/CLK swing between 0.2V and 3.0V with a transi-

tion time of 20ns maximum. For X1/CLK, this swing is between 0.2V and 4.4V. All time measurements are referenced at input voltages of

0.2V and 3.0V and output voltages of 0.8V and 2.0V, as appropriate.

6. See Figure 18 for test conditions for outputs.

7. Tests for open drain outputs are intended to guarantee switching of the output transistor. To include noise margin this response is measured

from the switching signal midpoint to 0.2 V above the required output level.

8. Execution of the valid command (after it is latched) requires a minimum of three rising edges of X1 (see Figure 19).

9. These values were no explicitly tested; they are guaranteed by design and characterization data.

10.X1/CLK and X2 are not tested with a crystal installed.

11. X1/CLK frequency must be at least as fast as the faster of the receiver or transmitter data rate.

12.The X1 clock drives DTACKN, Baud Rate Generator, command register and the update of the FIFO fill level encoders. The Command

Register requires three X1 clocks between two commands; FIFO fill level encoding requires 2.5 to 3.5 X1 cycles.

13.The 68562 bus interface may be operated in two modes; a 68000 compatible mode with automatic DTACK generation and a short chip

select mode. DTACKN should not be used externally in the short chip select mode. The DTACKN signal is generated by the assertion of

the chip select, and data is latched by assertion of DTACKN or by de-assertion of the chip select, whichever comes first. In single address

DMA, the DTACK signal will be de-asserted by the assertion of the DTCN or from the de-assertion of the TxDAKN, whichever occurs first.

14.Also includes X2/IDCN pin in IDC mode.

15.In case of 3-state output, output levels V

+ 0.2 are considered float or high impedance.

16.V

O

= 0 to V

CC

, Rx/Tx at 10MHz and X1 at 10MHz

pF

pF

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC68C562 | CMOS dual universal serial communications controller (CDUSCC)(CMOS 雙通用串行通信控制器(CDUSCC)) |

| SC68C562A8A | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 50 psi, Absolute, flush mount with flange, 10 Vdc excitation |

| SC68C562C1A | CMOS dual universal serial communications controller CDUSCC |

| SC68C562C1N | CMOS dual universal serial communications controller CDUSCC |

| SC80C451ACN64 | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC68C562C1A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS dual universal serial communications controller CDUSCC |

| SC68C562C1N | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS dual universal serial communications controller CDUSCC |

| SC68C652B | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:5 V, 3.3 V and 2.5 V dual UART, 5 Mbit/s (max.) with 32-byte FIFOs, IrDA encoder/decoder, and 68 mode mP interface |

| SC68C652BIB48 | 功能描述:UART 接口集成電路 2.5V-5V 2CH UART 32B FIFO MOT RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC68C652BIB48,128 | 功能描述:UART 接口集成電路 2.5V-5V 2CH UART 32B RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。