- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄271551 > SD-14595D1-245Z (DATA DEVICE CORP) SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 PDF資料下載

參數(shù)資料

| 型號: | SD-14595D1-245Z |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 位置變換器 |

| 英文描述: | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| 封裝: | DDIP-36 |

| 文件頁數(shù): | 10/14頁 |

| 文件大?。?/td> | 416K |

| 代理商: | SD-14595D1-245Z |

5

SOLID-STATE BUFFER INPUT PROTECTION — TRANSIENT

VOLTAGE SUPPRESSION

The solid-state signal and reference inputs are true differential

inputs with high ac and dc common rejection, so most applica-

tions will not require units with isolation transformers. Input

impedance is maintained with power off. The recurrent ac peak +

dc common mode voltage should not exceed the values in

TABLE 2.

REFERENCE

OSCILLATOR

PARALLEL

DATA

SD-14595/96/97

STATOR

ROTOR

S3

S1

S2

S1

S3

LBE

HBE

R2

R1

LO

HI

RH

VEL (VELOCITY)

INH (INHIBIT)

CB (COUNT)

RL

S4

REFERENCE

OSCILLATOR

PARALLEL

DATA

STATOR

ROTOR

S3

S1

S2

S1

S3

LBE

HBE

R4

R2

LO

HI

RH

VEL (VELOCITY)

INH (INHIBIT)

CB (COUNT)

RL

S4

RD-14595/96/97

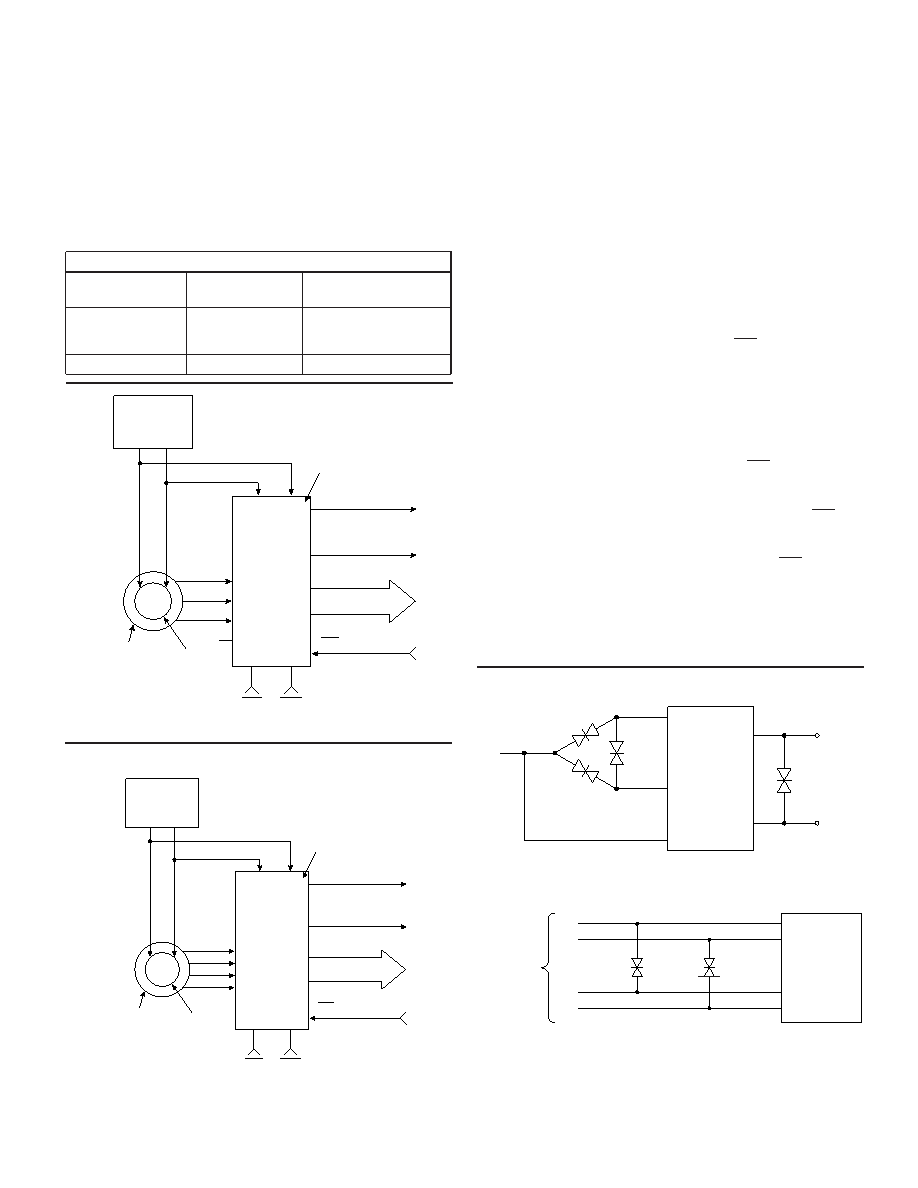

FIGURE 4. SYNCHRO INPUT CONNECTION DIAGRAM

FIGURE 5. RESOLVER INPUT CONNECTION DIAGRAM

90 V line-to-line systems may have voltage transients which

exceed the 500 V specification listed.

These transients can

destroy the thin-film input resistor network in the hybrid.

Therefore, 90 V L-L solid-state input modules may be protected

by installing voltage suppressors as shown. Voltage transients

are likely to occur whenever synchro or resolver are switched on

and off. For instance a 1000 V transient can be generated when

the primary of a CX or TX driving a synchro or resolver input is

opened. See FIGURE 6.

INTERFACING - DIGITAL OUTPUTS AND CONTROLS

DIGITAL INTERFACE

The digital interface circuitry performs three main functions:

1. Latches the output bits during an Inhibit (INH) command allow-

ing stable data to be read out of the SD-14595/96/97.

2. Furnishes parallel tri-state data formats.

3. Acts as a buffer between the internal CMOS logic and the

external TTL logic.

In the SD-14595/96/97, applying an Inhibit (INH) command will

lock the data in the inhibit transparent latch without interfering

with the continuous tracking of the converter’s feedback loop.

Therefore the digital angle

φ is always updated and the INH can

be applied for an arbitrary amount of time. The Inhibit

Transparent Latch and the 50 ns delay are part of the inhibit cir-

cuitry. For further information see the INHIBIT (INH, PIN 13)

paragraph.

HYBRID

S3

S2

S1

RH

RL

CR1

CR2

S1

FOR 90 V SYNCHRO INPUTS

1N6071A

CR3

S2

S3

CR1, CR2, and CR3 are 1N6136A, bipolar transient voltage suppressors

or equivalent.

HYBRID

S3

S2

S1

S4

FOR 90 V RESOLVER INPUTS

CR4

CR5

S3

S2

S1

S4

90 V L-L

RESOLVER

INPUT

CR4 and CR5 are 1N6136A, bipolar transient voltage suppressors or equivalent.

FIGURE 6. CONNECTIONS FOR VOLTAGE

TRANSIENT SUPPRESSORS

COMMON MODE

MAXIMUM

100 V

30 V Peak

180 V Peak

250 V Peak

150 V

11.8 VL-L

90 VL-L

Reference

MAX TRANSIENT PEAK

VOLTAGE

1 VL-L

INPUT

TABLE 2.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SD-14595D1-245 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14595D1-252K | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14595D1-252L | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14595D1-252S | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| SD-14595D1-252Y | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SD-14595D1-302 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14595D1-304 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14595D1-305 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14595D2-102 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

| SD-14595D2-104 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchro-to-Digital Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。