- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372134 > SDM863R 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS PDF資料下載

參數(shù)資料

| 型號: | SDM863R |

| 英文描述: | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| 中文描述: | 16單端/ 8差分輸入12位數(shù)據(jù)采集系統(tǒng) |

| 文件頁數(shù): | 7/27頁 |

| 文件大?。?/td> | 256K |

| 代理商: | SDM863R |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

SDM862/863/872/873

7

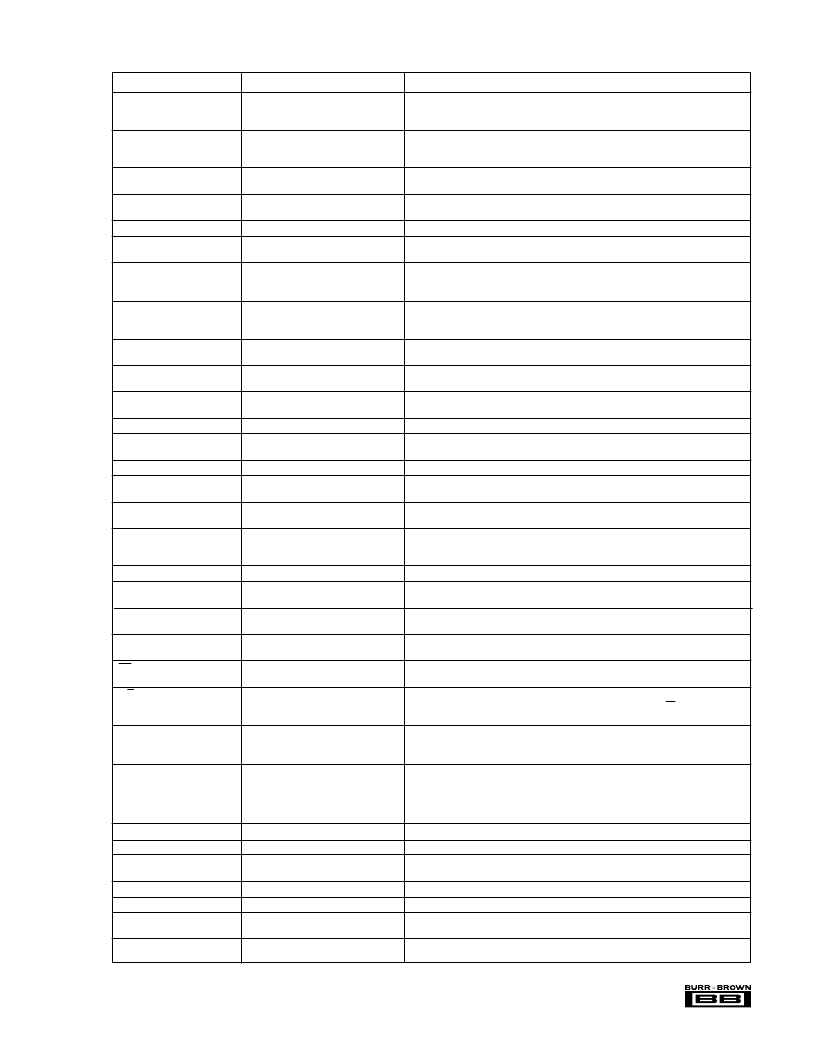

PIN DESIGNATION

DEFINITION

COMMENTS

SDM8X2 = SDM862 OR SDM872

CH0 to CH15

CH0 to CH7 (+, –)

(PINS 40 to 47, 54 to 61)

Channel Inputs

Analog Inputs (Total 16) for single-ended and differential operation. Unused

inputs must be connected to analog common.

MUX OUT+/AMP IN+

MULTIPLEXER “HI” OUTPUT

On the SDM8X2 this is the multiplexer output. On the SDM8X3 it is the

output of the positive selected inputs. It is connected internally to the

positive input of the instrumentation amplifier.

(PIN 65)

MUXOUT (Pin 67)

MULTIPLEXER “LO” OUTPUT

This pin is used on the SDM8X3 only. It should be connected to the negative

input of the instrumentation amplifier.

AMP IN (Pin 66)

Negative input of instrumentation

amplifier

On the SDM8X2 this should be connected to analog common. On the

SDM8X3 it should be connected to Muxout—(Pin 67).

AMP OUT (Pin 1)

Output of instrumentation amplifier

This pin should be connected to the input of the S/H amplifier (Pin 39).

AMP SENSE (Pin 68)

Output sense line of instrumentation

amplifier

This pin will normally be connected direct to AMP OUT (Pin 1).

AMP REF (Pin 2)

Reference for amplifier output

This pin will normally be connected to analog common. Care should be

taken to minimize tracking and contact resistance to analog common to

optimize system accuracy.

S/H OUT (Pins 35/37)

Output of sample/hold amplifier

Two pins are provided to facilitate a guard ring around the hold capacitor

pin. These pins should be connected to either ADC in (20V) or ADC in (10V)

depending on the desired range.

HOLD CAP (Pin 36)

Connection for hold capacitor on

S/H amplifier

The tracking to the hold capacitor should be as short as possible and a

guard ring employed using Pins 35 and 37.

ADC IN (20V); ADC IN (10V)

(Pins 21, 22)

Inputs to A/D converter

Connect to S/H amplifier output. Use appropriate pin for desired range.

RG, G10, G100

(Pins 62, 63, 64)

Gain settling pins on instrumentation

amplifier

For Gain = 1, no connections. For Gain = 10, connect G10 to RG.

For Gain = 100, connect G100 to RG.

REF OUT (PIN 26)

10V Reference voltage

This is the reference voltage for the A/D converter.

REF IN, BIP OFF

(Pins 24, 23)

Reference input and offset input to

A/D converter

Connect trim potentiometers (or select-on-test resistors) to these pins for

unipolar or bipolar operation as shown in Figures 12, 13.

S/H IN (Pin 39)

Input to sample/hold amplifier

Connect to amp out (Pin 1).

MUX ENABLE (Pin 48)

Multiplex enable/disable

Logic ‘1’ on this pin will enable a selected channel on the internal

multiplexer. Logic ‘0’ de-selects all channels.

MUX ADD0 to MUX ADD3

(Pins 49 to 52)

Address inputs for channel selection

These address lines select a particular channel as specified in Figure 24.

S/H CONT (Pin 33)

Track/Hold control on S/H amplifier

Logic ‘1’ holds an analog value for conversion by the A/D converter. This line

may be controlled by the status (Pin 6) of the converter to simplify external

timing control.

S/H COM (Pin 34)

Reference for S/H logic control

Connect to digital common.

D0 to D11 (Pins 7 to 18)

3-state digital outputs

The 12- or 8-bit result of a conversion is available as output on these pins

(D0-LSB, D11-MSB).

STATUS (Pin 6)

Status of A/D conversion

This output is at logic ‘1’ while the internal A/D converter is carrying out a

conversion. This pin may be used to directly control the S/H amplifier.

CE (Pin 28)

Chip enable

This input must be at logic ‘1’ to either initiate a conversion or read output

data (see Figures 10, 17, 18, 19, 20).

CS (Pin 31)

Chip select

This input must be at logic ‘0’ to either initiate a conversion or read output

data (see Figures 10, 17, 18, 19, 20).

R/C (Pin 29)

Read/convert

Data can be read when this pin is logic ‘1’ or a conversion can be initiated

when this pin is logic ‘0’. This pin is typically connected to the R/W control

line of a microprocessor-based system (see Figures 10, 17, 18, 19, 20).

DATA MODE (Pin 30)

Select 12- or 8-Bit Data

When data mode is at logic ‘1’ all 12 output data bits are enabled

simultaneously. When data mode is at logic ‘0’ MSBs and LSBs are

controlled by byte select (Pin 32).

BYTE SELECT (Pin 32)

Byte address, short cycle

When reading output data, byte select at logic ‘0’ enables the 8 MSBs. Byte

select at logic ‘1’ enables the 4 LSBs. The 4 LSBs can therefore be connected

to four of the MSB lines for inter-connection to an 8-bit bus. In start convert

mode, logic ‘0’ enables a 12-bit conversion while logic ‘1’ will short cycle the

conversion to 8 bits (see Figure 10).

+15V(1), +15V(2)(Pins 3, 27)

Power Supply

Connect to +15V supply using decoupling as indicated in Figures 15, 16.

–15V(1), –15V(2)(Pins 4, 20)

Power Supply

Connect to –15V supply using decoupling as indicated in Figures 15, 16.

ACOM(2) (Pin 25)

Analog Common

Analog common connection. Note that a common (including digital

common) should be connected together at one point close to the device.

DCOM (1) (Pin 53)

Reference for MUX logic control.

Connect to digital common.

+5V (Pin 5)

Logic power supply

Connect to +5V digital supply line with decoupling as in Figures 15, 16.

DCOM(2) (Pin 19)

Reference for A/D converter control

lines

Connect to S/H common at one point close to device.

NC (Pin 38)

No internal connection

相關PDF資料 |

PDF描述 |

|---|---|

| SDM863S | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872 | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872A | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872B | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872J | 16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SDM863S | 制造商:BB 制造商全稱:BB 功能描述:16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872 | 制造商:BB 制造商全稱:BB 功能描述:16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872A | 制造商:BB 制造商全稱:BB 功能描述:16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872B | 制造商:BB 制造商全稱:BB 功能描述:16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

| SDM872J | 制造商:BB 制造商全稱:BB 功能描述:16 Single Ended/8 Differential Input 12-BIT DATA ACQUISITION SYSTEMS |

發(fā)布緊急采購,3分鐘左右您將得到回復。