- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378697 > SM5865AM (Seiko NPC Corporation) D/A Converter PDF資料下載

參數(shù)資料

| 型號: | SM5865AM |

| 廠商: | Seiko NPC Corporation |

| 英文描述: | D/A Converter |

| 中文描述: | D / A轉(zhuǎn)換 |

| 文件頁數(shù): | 11/17頁 |

| 文件大小: | 130K |

| 代理商: | SM5865AM |

pemnr

SM5865AM

NIPPON PRECISION CIRCUITS—11

System Clock Divider (CKDVN)

The SM5865AM has a built-in divide-by-2 system

clock frequency divider. The divider enables the

internal system clock to operate at half the input fre-

quency, for example when the external master clock

input frequency is high.

System Reset (RSTN)

The device should be reset in the following cases.

I

At power ON

I

When the system clock CKI stops, or other abnor-

malities occur.

The device is reset by applying a LOW-level pulse

on RSTN.

Audio Data Input (DI, BCKI, WCKI, IWSL)

Input data format

The audio data is input in MSB-first, 2s-comple-

ment, 24-bit/20-bit serial format. The input word bit

length is selected by IWSL, 24-bit when HIGH or

open circuit, and 20-bit when LOW.

Jitter-free function

Serial input data bits on DI are read into an SIPO

register (serial-to-parallel converter register) on the

rising edge of the bit clock BCKI where the serial

data is converted into parallel data. The internal par-

allel data control timing is derived from the system

clock, and is not affected by any jitter on the input

data clocks (WCKI and BCKI). After a reset opera-

tion is released when RSTN goes HIGH, the internal

timing and the WCKI input timing are phase com-

pared on the first and subsequent WCKI falling

edges and the comparison result is used to perform

timing adjustment to maintain the word boundary

relationship between the internal timing and the

WCKI clock.

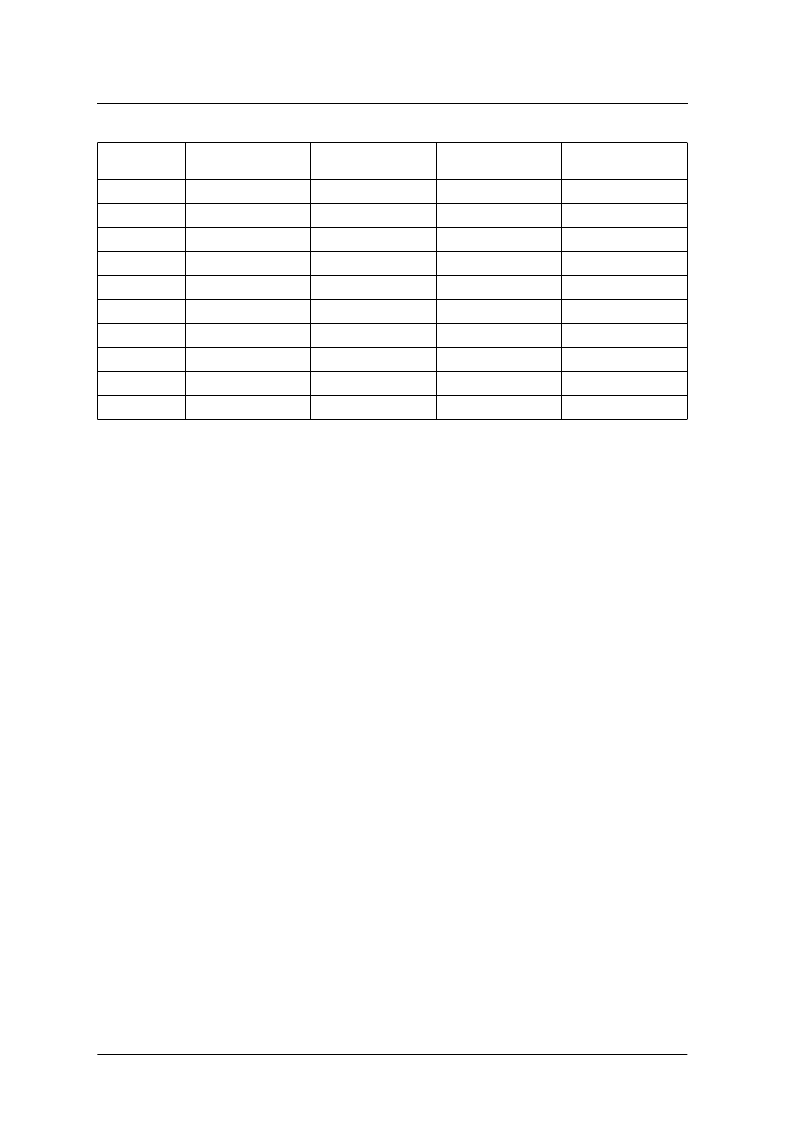

88.2 kHz

11.2896 MHz (128fs)

16fs

2

4

88.2 kHz

16.9344 MHz (192fs)

24fs

3

6

88.2 kHz

22.5792 MHz (256fs)

32fs

4

8

88.2 kHz

33.8688 MHz (384fs)

48fs

6

12

96 kHz

12.288 MHz (128fs)

16fs

2

4

96 kHz

18.432 MHz (192fs)

24fs

3

6

96 kHz

24.576 MHz (256fs)

32fs

4

8

96 kHz

36.864 MHz (384fs)

48fs

6

12

192 kHz

24.576 MHz (128fs)

16fs

2

4

192 kHz

36.864 MHz (192fs)

24fs

3

6

1. When CKDVN = LOW, the systemclock frequency f

CKI

is halved, so the values shown are half the input frequency required for the same sampling rate

and internal factors.

Table 2. System clock frequencies (CKDVN = HIGH)

fs

System clock frequency

1

f

CKI

Noise shaper operating

rate

Internal factor

(8fs input)

Internal factor

(4fs input)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SM5865CM | D/A Converter for Digital Audio |

| SM5866AS | D/A Converter for DSD and PCM |

| SM5871A | CMOS LSI(Digital Audio D/A Converter) |

| SM5872 | CMOS LSI(Digital D/A Converters with Built-in Digital Filters |

| SM5872A | CMOS LSI(Digital D/A Converters with Built-in Digital Filters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SM5865BM | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:D/A Converter for Digital Audio |

| SM5865CM | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:D/A Converter for Digital Audio |

| SM5866AS | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:D/A Converter for DSD and PCM |

| SM586A181LEVCN | 制造商:Schneider Electric 功能描述:Proximity Sensor Ultrasonic |

| SM5871A | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:CMOS LSI(Digital Audio D/A Converter) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。