- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373439 > SN74AHCT161 (Texas Instruments, Inc.) 4-Bit Synchronous Binary Counters(4位二進制同步計數(shù)器) PDF資料下載

參數(shù)資料

| 型號: | SN74AHCT161 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 通用總線功能 |

| 英文描述: | 4-Bit Synchronous Binary Counters(4位二進制同步計數(shù)器) |

| 中文描述: | 4位同步二進制計數(shù)器(4位二進制同步計數(shù)器) |

| 文件頁數(shù): | 1/10頁 |

| 文件大小: | 224K |

| 代理商: | SN74AHCT161 |

SN54AHCT161, SN74AHCT161

4-BIT SYNCHRONOUS BINARY COUNTERS

SCLS368A – MAY 1997 – REVISED JUNE 1997

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Inputs Are TTL-Voltage Compatible

EPIC

(Enhanced-Performance Implanted

CMOS) Process

Internal Look-Ahead for Fast Counting

Carry Output for n-Bit Cascading

Synchronous Counting

Synchronously Programmable

Package Options Include Plastic

Small-Outline (D), Shrink Small-Outline

(DB), Thin Shrink Small-Outline (PW), and

Ceramic Flat (W) Packages, Ceramic Chip

Carriers (FK), and Standard Plastic (N) and

Ceramic (J) 300-mil DIPs

description

These synchronous, presettable counters feature

an internal carry look-ahead for application in

high-speed counting designs. The ’AHCT161 are

4-bit binary counters. Synchronous operation is

provided by having all flip-flops clocked

simultaneously so that the outputs change

coincident with each other when so instructed by

the count-enable (ENP, ENT) inputs and internal

gating. This mode of operation eliminates the

output counting spikes that are normally

associated with synchronous (ripple-clock)

counters. A buffered clock (CLK) input triggers the

four flip-flops on the rising (positive-going) edge of

the clock waveform.

These counters are fully programmable; that is, they can be preset to any number between 0 and 9 or 15. As

presetting is synchronous, setting up a low level at the load input disables the counter and causes the outputs

to agree with the setup data after the next clock pulse, regardless of the levels of the enable inputs.

The clear function for the ’AHCT161 is asynchronous. A low level at the clear (CLR) input sets all four of the

flip-flop outputs low, regardless of the levels of the CLK, load (LOAD), or enable inputs.

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without

additional gating. Instrumental in accomplishing this function are ENP, ENT, and a ripple-carry (RCO) output.

Both ENP and ENT must be high to count, and ENT is fed forward to enable RCO. Enabling RCO produces a

high-level pulse while the count is maximum (9 or 15 with Q

A

high). This high-level overflow ripple-carry pulse

can be used to enable successive cascaded stages. Transitions at ENP or ENT are allowed, regardless of the

level of CLK.

These counters feature a fully independent clock circuit. Changes at control inputs (ENP, ENT, or LOAD) that

modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of

the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the

stable setup and hold times.

P

Copyright

1997, Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

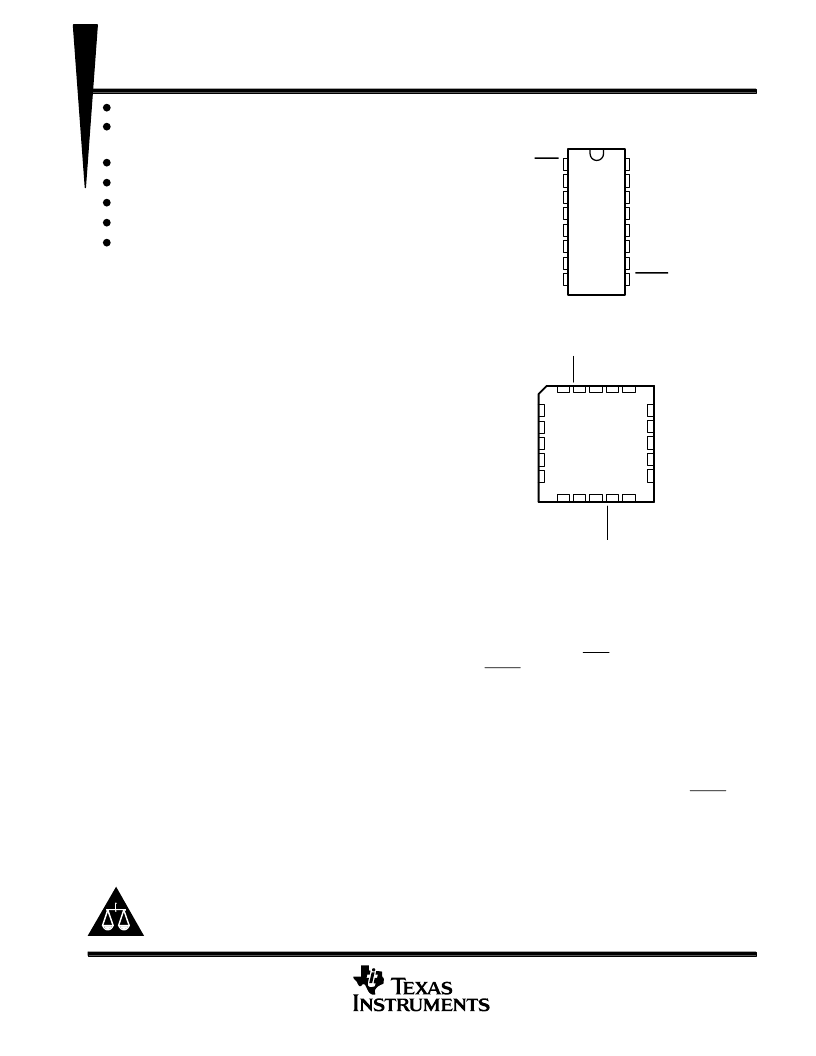

SN54AHCT161 . . . J OR W PACKAGE

SN74AHCT161 . . . D, DB, N, OR PW PACKAGE

(TOP VIEW)

SN54AHCT161 . . . FK PACKAGE

(TOP VIEW)

NC – No internal connection

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

CLR

CLK

A

B

C

D

ENP

GND

V

CC

RCO

Q

A

Q

B

Q

C

Q

D

ENT

LOAD

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

Q

A

Q

B

NC

Q

C

Q

D

A

B

NC

C

D

C

C

N

L

E

R

E

G

N

V

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54AHCT16240WD | 16-BIT BUFFERS/DRIVERS WITH 3-STATE OUTPUTS |

| SN74AHCT16240DGG | 16-BIT BUFFERS/DRIVERS WITH 3-STATE OUTPUTS |

| SN74AHCT16240DGV | 16-BIT BUFFERS/DRIVERS WITH 3-STATE OUTPUTS |

| SN54AHCT16240 | 16-Bit Buffers/Line Drivers With 3-State Outputs(16位緩沖器/驅(qū)動器(三態(tài)輸出)) |

| SN54AHCT16244 | 16-Bit Buffers/Line Drivers With 3-State Outputs(16位緩沖器/驅(qū)動器(三態(tài)輸出)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74AHCT16240DGGR | 功能描述:緩沖器和線路驅(qū)動器 16bit RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| SN74AHCT16240DGVR | 功能描述:緩沖器和線路驅(qū)動器 16bit RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| SN74AHCT16240DL | 功能描述:緩沖器和線路驅(qū)動器 16bit RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| SN74AHCT16240DLG4 | 功能描述:緩沖器和線路驅(qū)動器 16-Bit Buffer/Driver With 3-State Outputs RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| SN74AHCT16240DLR | 功能描述:緩沖器和線路驅(qū)動器 16-Bit Buffer/Driver With 3-State Outputs RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。