- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376417 > SN74LVCH16901DGG (Texas Instruments, Inc.) 18-BIT UNIVERSAL BUS TRANSCEIVER WITH PARITY GENERATORS/CHECKERS PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LVCH16901DGG |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 18-BIT UNIVERSAL BUS TRANSCEIVER WITH PARITY GENERATORS/CHECKERS |

| 中文描述: | 18位通用總線收發(fā)器奇偶產(chǎn)生器/ |

| 文件頁數(shù): | 2/11頁 |

| 文件大小: | 155K |

| 代理商: | SN74LVCH16901DGG |

SN74LVCH16901

18-BIT UNIVERSAL BUS TRANSCEIVER

WITH PARITY GENERATORS/CHECKERS

SCES145A – OCTOBER 1998 – REVISED MAY 1999

2

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

description (continued)

Inputs can be driven from either 3.3-V or 5-V devices. This feature allows the use of these devices as translators

in a mixed 3.3-V/5-V system environment.

To ensure the high-impedance state during power up or power down, OE should be tied to V

CC

through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

This device is fully specified for partial-power-down applications using I

off

. The I

off

circuitry disables the outputs,

preventing damaging current backflow through the device when it is powered down.

The SN74LVCH16901 is characterized for operation from –40

°

C to 85

°

C.

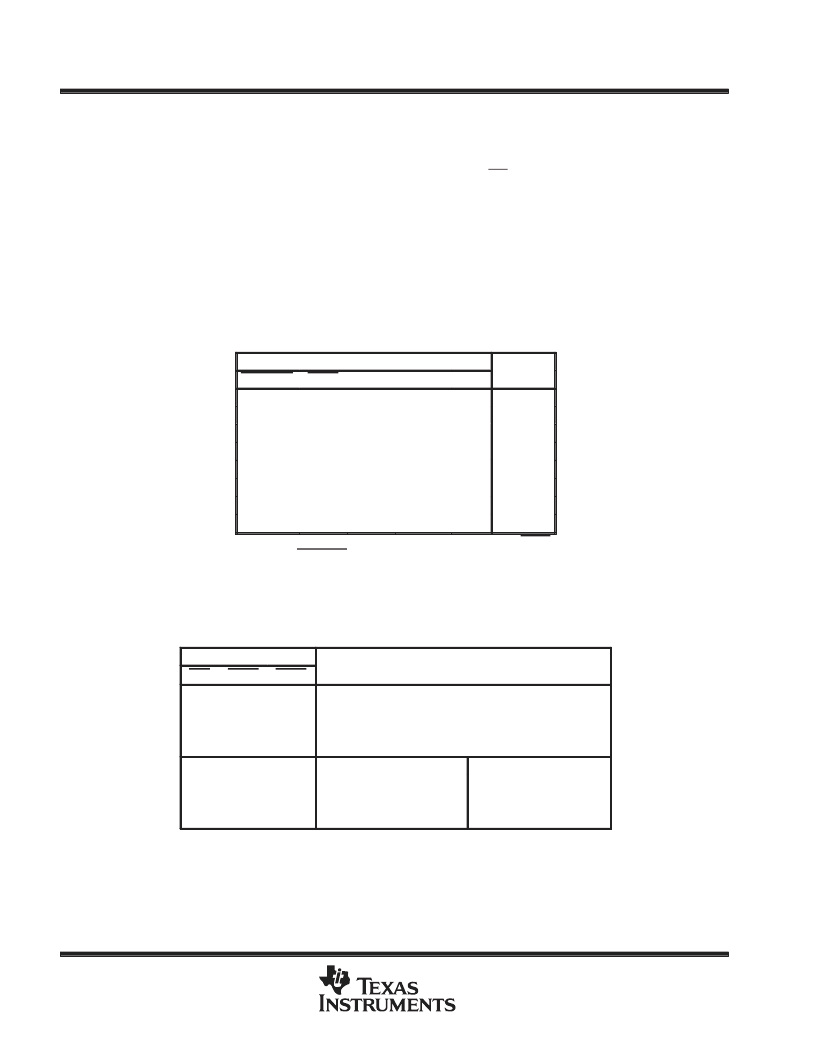

Function Tables

FUNCTION

INPUTS

LEAB

OUTPUT

B

CLKENAB

OEAB

CLKAB

A

X

H

X

X

X

Z

X

L

H

X

L

L

X

L

H

X

H

H

H

L

L

X

↑

↑

L

X

B0

L

L

L

L

L

L

L

L

H

H

L

L

L

X

B0

B0§

L

L

L

H

X

A-to-B data flow is shown: B-to-A flow is similar, but uses OEBA,

LEBA, and CLKENBA.

Output level before the indicated steady-state input conditions were

established

§Output level before the indicated steady-state input conditions were

established, provided that CLKAB was low before LEAB went low

PARITY ENABLE

INPUTS

OPERATION OR FUNCTION

SEL

OEBA

OEAB

L

H

L

Parity is checked on port A and is generated on port B.

L

L

H

Parity is checked on port B and is generated on port A.

L

H

H

Parity is checked on port B and port A.

L

L

L

Parity is generated on port A and B if device is in FF mode.

H

L

L

QA data to B, QB data to A

QB data to A

QA data to B

Isolation

H

L

H

Parity functions are disabled;

device acts as a standard

18-bit registered transceiver.

18 bit registered transceiver.

H

H

H

H

L

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN75175 | Quadruple Differential Line Receiver 16-SOIC 0 to 70 |

| SN75175D | Quadruple Differential Line Receiver 16-SOIC 0 to 70 |

| SN75175N | Quadruple Differential Line Receiver 16-SOIC 0 to 70 |

| SN761678BDBT | TV TUNER IC |

| SN761678BDBTG4 | TV TUNER IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LVCH16901DGGR | 功能描述:通用總線函數(shù) 12-Bit 1-Of-3 FET Mltplxr/Demltplxr RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開啟電阻(最大值): 傳播延遲時(shí)間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVCH16952ADGGR | 功能描述:總線收發(fā)器 16bit Reg RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVCH16952ADGVR | 功能描述:總線收發(fā)器 16bit Reg RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVCH16952ADL | 功能描述:總線收發(fā)器 16bit Reg RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVCH16952ADLG4 | 功能描述:總線收發(fā)器 16bit Reg RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。