- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378703 > SP5054KGDPAS (Mitel Networks Corporation) 2.6GHz 3-Wire BUS Controlled Synthesiser PDF資料下載

參數(shù)資料

| 型號(hào): | SP5054KGDPAS |

| 廠(chǎng)商: | Mitel Networks Corporation |

| 英文描述: | 2.6GHz 3-Wire BUS Controlled Synthesiser |

| 中文描述: | 2.6GHz的3線(xiàn)總線(xiàn)控制合成器 |

| 文件頁(yè)數(shù): | 4/9頁(yè) |

| 文件大小: | 279K |

| 代理商: | SP5054KGDPAS |

4

SP5054

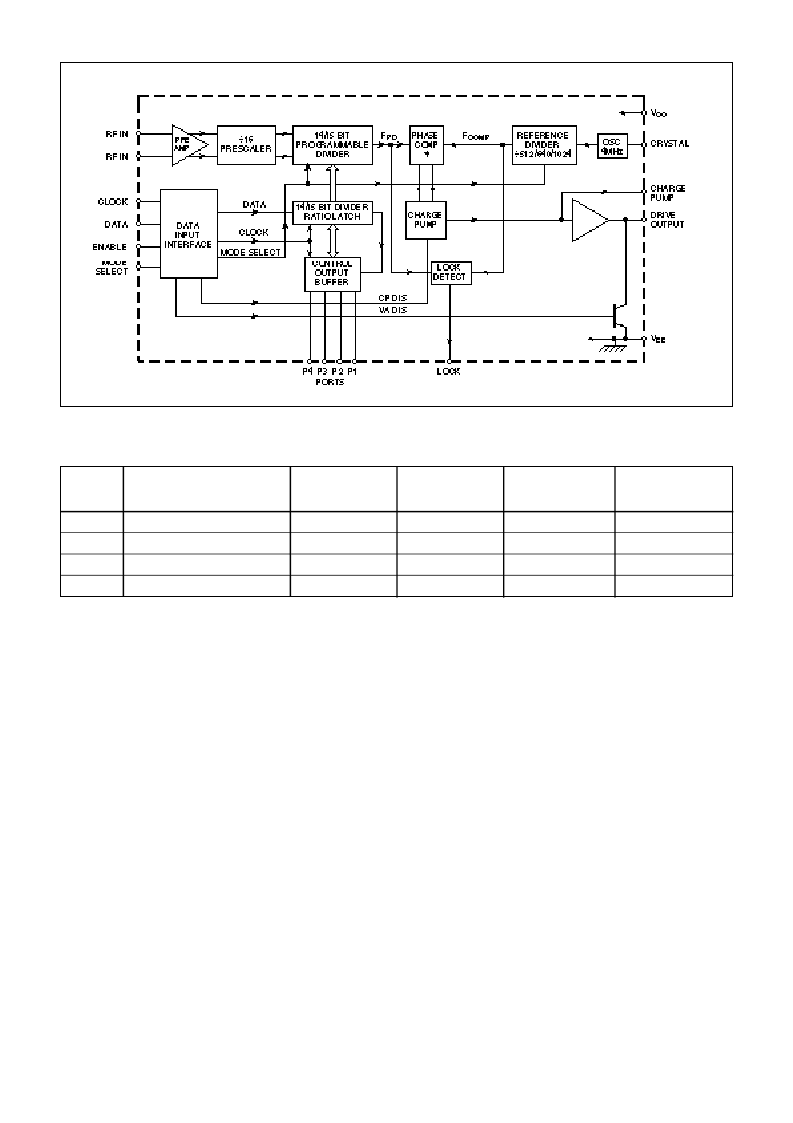

Fig. 3 Block diagram of SP5054

FUNCTIONAL DESCRIPTION

The SP5054 contains all the elements necessary, with the

exception of reference crystal, loop filter and external high

voltage transistor, to control a voltage controlled local oscilla-

tor, so forming a PLL frequency synthesised source.

The system is controlled by a microprocessor via a stand-

ard Data, Clock and Enable three-wire data bus.

The data load normally consists of a single word, which

contains the frequency and port information, and is only

transferred to the internal data shift register during an enable

high period.

The clock input is disabled during enable low periods. New

data words are only accepted by the internal data buffers from

the shift register on a negative transition of the Enable, so

giving improved fine tune facility for digital AFC etc.

The data sequence and timing follows the format shown in

Fig. 4.

The frequency is set by loading the programmable divider

with the required 14/15 bit divisor word. The output of this

divider, F

PD

, is fed to the phase comparator where it is

compared in phase and frequency domain to the internally

generated comparison frequency, F

.

F

COMP

is obtained by dividing the output of an on-chip

crystal controlled oscillator. The crystal frequency used is

generally 4MHz, which gives an F

COMP

of 3·90625/6·25/

7·8125kHz and, when multiplied back up to the synthesised

LO, gives a minimum step size of 62·5/100/125kHz, respec-

tively.

The programmable divider is preceded by an input RF

preamplifier and high speed, low radiation prescaler. The

preamplifier is arranged to be self oscillating, so giving excel-

lent input sensitivity.

The SP5054 contains an improved lock detect circuit

which generates a flag when the loop has attained lock. ‘In

lock’ is indicated by high impedance state.

The SP5054 contains 4 general purpose open collector

outputs, ports P1-P4, which are capable of sinking at least

10mA. These outputs are set by the remaining four bits within

the normal data word.

NOTES ON PIN COMPATIBILITY

The SP5054 may be used in SP5055 applications which

require 3-wire bus as opposed to I

2

C bus data format. In

SP5055 applications where the reference crystal is grounded

to pin 3, a small modification is required to ground the crystal

as shown in Fig. 5.

Appropriate connections must also be made to the Mode

Select input (see Table 1). In Mode 3, The SP5054 is pro-

gramming compatible with the Toshiba TD6380, in Modes 0

and 2 with the TD6381 and in Mode 1 with the TD6382.

Mode Select input voltage

0·925V

CC

to V

CC

0·675V

CC

to 0·825V

CC

Open circuit

0V to 0·325 V

CC

Table 1 SP5054 modes of operation. * Frequencies stated apply when using a 4MHz crystal.

Programmable

divider bit

length

14

15

15

15

Mode

3

2

1

0

Reference

divider

ratio

512

512

1024

640

Frequency

step size

(kHz)

*

125

125

62·5

100

Maximum

operating

frequency (GHz)

*

2·0479

2·5

2·0479

2·5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SP5054 | 2.6GHz 3-Wire BUS Controlled Synthesiser |

| SP5054SKGMPAS | 2.6GHz 3-Wire BUS Controlled Synthesiser |

| SP5055 | 2.6GHz Bidirectional I2C BUS Controlled Synthesiser |

| SP5055SMP | 2.6GHz Bidirectional I2C BUS Controlled Synthesiser |

| SP5070 | 2.GHz Fixed Modulus Frequency Synthesiser |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SP5054SKGMPAS | 制造商:MITEL 制造商全稱(chēng):Mitel Networks Corporation 功能描述:2.6GHz 3-Wire BUS Controlled Synthesiser |

| SP5055 | 制造商:MITEL 制造商全稱(chēng):Mitel Networks Corporation 功能描述:2.6GHz Bidirectional I2C BUS Controlled Synthesiser |

| SP5055SMP | 制造商:MITEL 制造商全稱(chēng):Mitel Networks Corporation 功能描述:2.6GHz Bidirectional I2C BUS Controlled Synthesiser |

| SP505A | 制造商:BLKBOX 功能描述: |

| SP505AB | 制造商:SIPEX 制造商全稱(chēng):Sipex Corporation 功能描述:WAN Multi-Mode Serial Transceiver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。