- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄193720 > SRM20V100SLBX7 128K X 8 STANDARD SRAM, 70 ns, PBGA32 PDF資料下載

參數(shù)資料

| 型號: | SRM20V100SLBX7 |

| 元件分類: | SRAM |

| 英文描述: | 128K X 8 STANDARD SRAM, 70 ns, PBGA32 |

| 封裝: | PLASTIC, CSP-32 |

| 文件頁數(shù): | 1/10頁 |

| 文件大?。?/td> | 138K |

| 代理商: | SRM20V100SLBX7 |

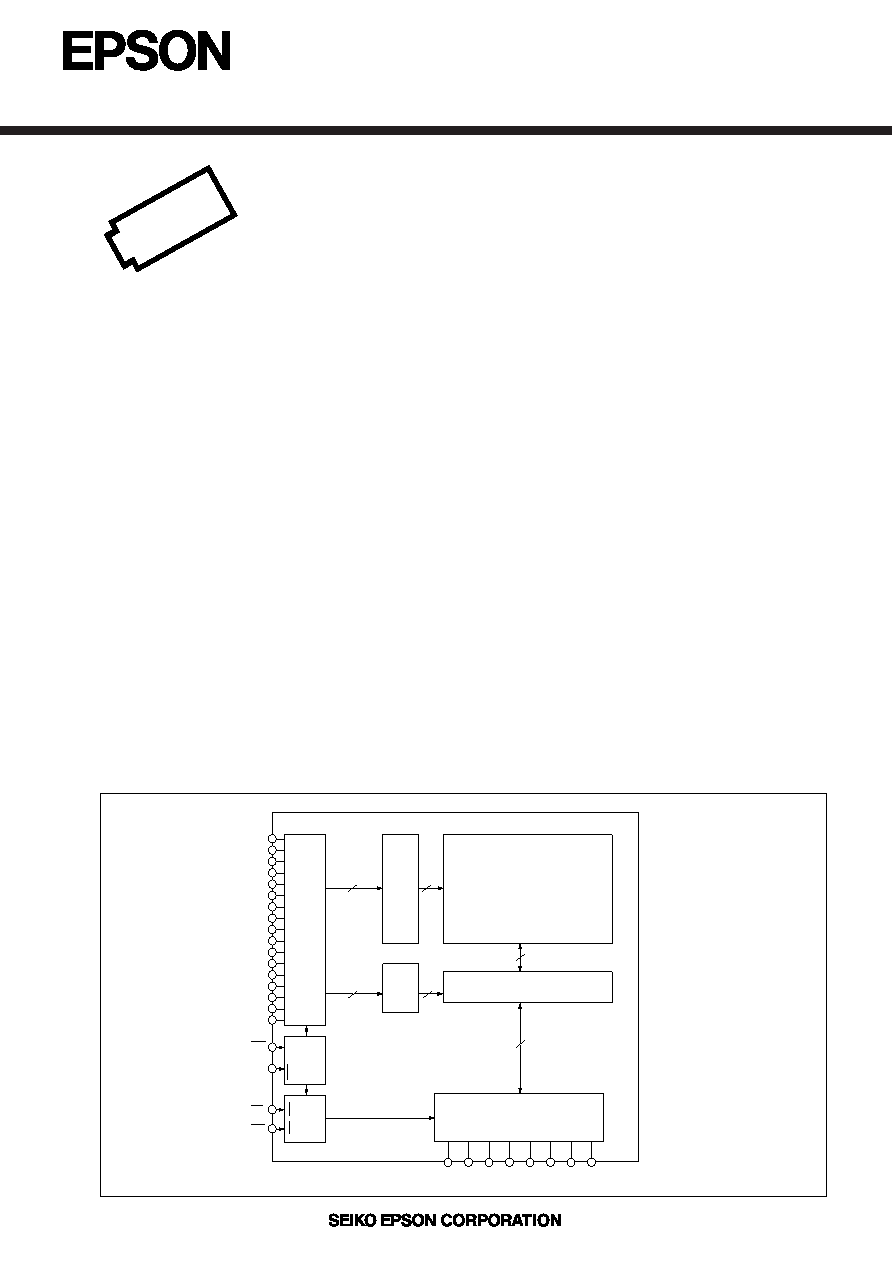

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

CS1

OE

WE

I/O Buffer

Column Gate

Memory Cell Array

1024

×128×8

128

×8

8

10

1024

7

128

I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 I/O8

A13

A15

A16

A14

CS2

Address

Buffer

X

Decoder

Y

Decoder

Chip

Control

CS1,

CS2

Chip

Control

OE,

WE

1M-Bit Static RAM

PF805-05

s DESCRIPTION

The SRM20V100LLMX7 / SLMX7 is an 131,072 words

×8-bit asynchronous, static, random access memory on a

monolithic CMOS chip. Its very low standby power requirement makes it ideal for applications requiring non-

volatile storage with back-up batteries. And –25 to 85

°C operating temperature range makes it ideal for portable

equipment. The asynchronous and static nature of the memory requires no external clock or refreshing circuit.

Both the input and output ports are TTL compatible and 3-state output allows easy expansion of memory capacity.

s FEATURES

q Wide temperature range ..... –25 to 85

°C

q Fast Access time ................. 70ns (Max.)

q Low supply current .............. standby: 0.6

A (Typ.): LL Version

0.5

A (Typ.): SL Version

operation: 8mA/1MHz (Typ.)

q Completely static ................. No clock required

q Supply voltage ..................... 2.7V to 3.6V

q TTL compatible inputs and outputs

q 3-state output with wired-OR capability

q Non-volatile storage with back-up batteries

q Package ................. SRM20V100LL(SL)MX7

SOP6-32pin (plastic)

SRM20V100LL(SL)TX7

TSOP ( I )-32pin (plastic)

SRM20V100LL(SL)RX7

TSOP ( I )-32pin-R1 (plastic)

SRM20V100LL(SL)KX7

Slim-TSOP ( I )-32pin (plastic)

SRM20V100LL(SL)YX7

Slim-TSOP ( I )-32pin-R1 (plastic)

SRM20V100LL(SL)BX7

CSP-32pin

s BLOCK DIAGRAM

Low

Voltage

Operation

Products

q Low Supply Voltage

q Wide Temperature Range

q Low Supply Current

q Access Time 70ns (2.7V)

q 131,072 Wordsx8-bit Asynchronous

SRM20V100LLMX7/SLMX7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SRMMCC-3-R | QUARTZ CRYSTAL RESONATOR, 0.032768 MHz |

| SRMMCC-1-R | QUARTZ CRYSTAL RESONATOR, 0.032768 MHz |

| SRMMCC-2-R | QUARTZ CRYSTAL RESONATOR, 0.032768 MHz |

| SRMP49-24.0M | QUARTZ CRYSTAL RESONATOR, 24 MHz |

| SRN5124 | 20 MHz - 200 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SRM20V100SLKX7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| SRM20V100SLMX7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| SRM20V100SLRX7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| SRM20V100SLTX7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| SRM20V100SLYX7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。