- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372305 > ST624XB-KIT STARTER KIT DATASHEET FOR ST624X PDF資料下載

參數(shù)資料

| 型號(hào): | ST624XB-KIT |

| 英文描述: | STARTER KIT DATASHEET FOR ST624X |

| 中文描述: | 入門(mén)套件小冊(cè)子的ST624X |

| 文件頁(yè)數(shù): | 12/74頁(yè) |

| 文件大小: | 733K |

| 代理商: | ST624XB-KIT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

12/74

ST62T46B/E46B

MEMORY MAP

(Cont’d)

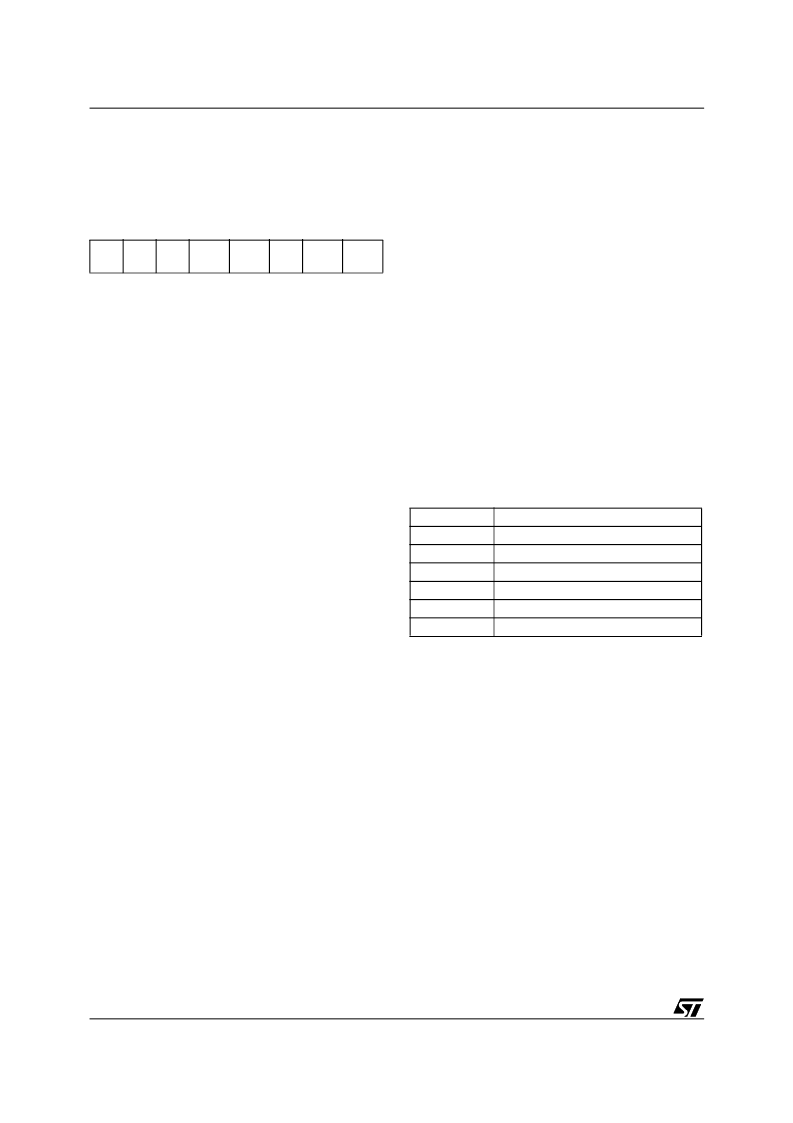

1.3.6 Data RAM/EEPROM Bank Register

(DRBR)

Address: CBh

—

Write only

Bit 7-5 = These bits are not used

Bit 4

-

DRBR4

. This bit, when set, selects RAM

Page 2.

Bit 3 -

DRBR3

. This bit, when set, selects RAM

Page 1.

Bit2. These bits are not used.

Bit 1 -

DRBR1

. This bit, when set, selects

EEPROM Page 1.

Bit 0 -

DRBR0

. This bit, when set, selects

EEPROM Page 0.

The selection of the bank is made by programming

the Data RAM Bank Switch register (DRBR regis-

ter) located at address CBh of the Data Space ac-

cording to Table 1. No more than one bank should

be set at a time.

The DRBR register can be addressed like a RAM

Data Space at the address CBh; nevertheless it is

a write only register that cannot be accessed with

single-bit operations. This register is used to select

the desired 64-byte RAM/EEPROM bank of the

Data Space. The number of banks has to be load-

ed in the DRBR register and the instruction has to

point to the selected location as if it was in bank 0

(from 00h address to 3Fh address).

This register is not cleared during the MCU initiali-

zation, therefore it must be written before the first

access to the Data Space bank region. Refer to

the Data Space description for additional informa-

tion. The DRBR register is not modified when an

interrupt or a subroutine occurs.

Notes

:

Care is required when handling the DRBR register

as it is write only. For this reason, it is not allowed

to change the DRBR contents while executing in-

terrupt service routine, as the service routine can-

not save and then restore its previous content. If it

is impossible to avoid the writing of this register in

interrupt service routine, an image of this register

must be saved in a RAM location, and each time

the program writes to DRBR it must write also to

the image register. The image register must be

written first, so if an interrupt occurs between the

two instructions the DRBR is not affected.

In DRBR Register, only 1 bit must be set. Other-

wise two or more pages are enabled in parallel,

producing errors.

Table 3. Data RAM Bank Register Set-up

7

0

-

-

-

DRBR4 DRBR3

-

DRBR1 DRBR0

DRBR

00h

01h

02h

08h

10h

other

ST62T46B/E46B

None

EEPROM Page 0

EEPROM Page 1

Not available

RAM Page 2

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST62E40BG1 | 8-BIT MICROCONTROLLER |

| ST62T45BQ6 | 8-BIT MICROCONTROLLER |

| ST6242B | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTROM. EPROM. LCD DRIVER. EEPROM. A/D CONVERTER AND 64 PINS |

| ST62E45BG1 | 8-BIT MICROCONTROLLER |

| ST62T40BQ6 | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST624XB-KIT/110 | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 ST624X Starter Kit RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| ST624XB-KIT/UK | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:ST62 KIT |

| ST6252 | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:8-BIT OTP/EPROM MCUs WITH A/D CONVERTER, AUTO-RELOAD TIMER AND EEPROM |

| ST6252BB1 | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:8-BIT OTP/EPROM MCUs WITH A/D CONVERTER, AUTO-RELOAD TIMER AND EEPROM |

| ST6252BB1/XXX | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。