- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98145 > ST72521AR7T1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | ST72521AR7T1/XXX |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, PLASTIC, TQFP-64 |

| 文件頁數(shù): | 126/199頁 |

| 文件大小: | 1979K |

| 代理商: | ST72521AR7T1/XXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁當前第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁

ST72521M/R/AR

32/199

SYSTEM INTEGRITY MANAGEMENT (Cont’d)

6.4.5 Register Description

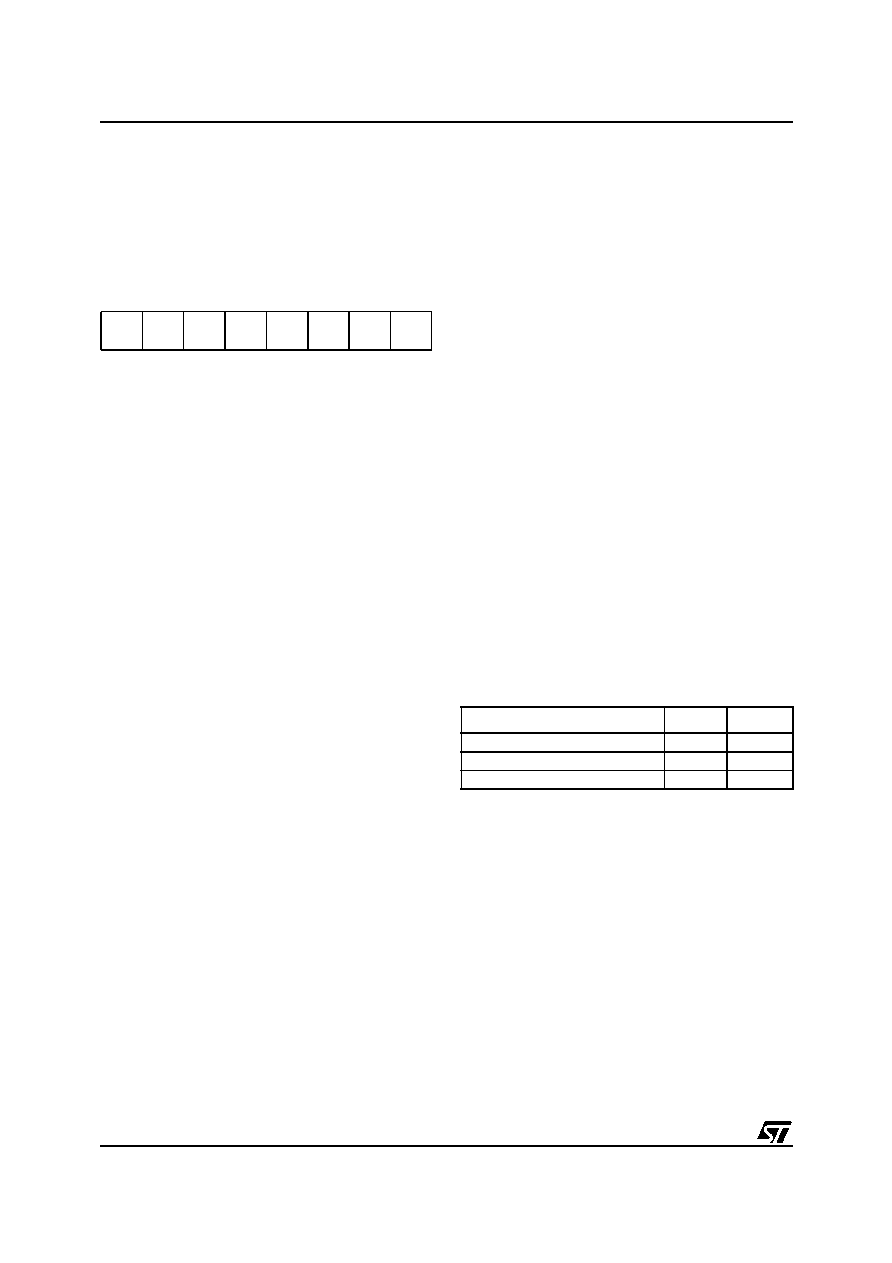

SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read /Write

Reset Value: 000x 000x (00h)

Bit 7 = AVDS

This bit is set and cleared by software. Voltage De-

tection is available only if the LVD is enabled by

option byte.

0: Voltage detection on VDD supply

1: Voltage detection on EVD pin

Bit 6 = AVDIE

Voltage Detector interrupt enable

This bit is set and cleared by software. It enables

an interrupt to be generated when the AVDF flag

changes (toggles). The pending interrupt informa-

tion is automatically cleared when software enters

the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

Bit 5 = AVDF

Voltage Detector flag

This read-only bit is set and cleared by hardware.

If the AVDIE bit is set, an interrupt request is gen-

erated when the AVDF bit changes value. Refer to

Figure 15 and to Section 6.4.2.1 for additional de-

tails.

0: VDD or VEVD over VIT+(AVD) threshold

1: VDD or VEVD under VIT-(AVD) threshold

Bit 4 = LVDRF

LVD reset flag

This bit indicates that the last Reset was generat-

ed by the LVD block. It is set by hardware (LVD re-

set) and cleared by software (writing zero). See

WDGRF flag description for more details. When

the LVD is disabled by OPTION BYTE, the LVDRF

bit value is undefined.

Bit 3 = Reserved, must be kept cleared.

Bit 2 = CSSIE

Clock security syst

.

interrupt enable

This bit enables the interrupt when a disturbance

is detected by the Clock Security System (CSSD

bit set). It is set and cleared by software.

0: Clock security system interrupt disabled

1: Clock security system interrupt enabled

When the CSS is disabled by OPTION BYTE, the

CSSIE bit has no effect.

Bit 1 = CSSD

Clock security system detection

This bit indicates that the safe oscillator of the

Clock Security System block has been selected by

hardware due to a disturbance on the main clock

signal (fOSC). It is set by hardware and cleared by

reading the SICSR register when the original oscil-

lator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the

CSSD bit value is forced to 0.

Bit 0 = WDGRF

Watchdog reset flag

This bit indicates that the last Reset was generat-

ed by the Watchdog peripheral. It is set by hard-

ware (watchdog reset) and cleared by software

(writing zero) or an LVD Reset (to ensure a stable

cleared state of the WDGRF flag when CPU

starts).

Combined with the LVDRF flag information, the

flag description is given by the following table.

Application notes

The LVDRF flag is not cleared when another RE-

SET type occurs (external or watchdog), the

LVDRF flag remains set to keep trace of the origi-

nal failure.

In this case, a watchdog reset can be detected by

software while an external reset can not.

CAUTION: When the LVD is not activated with the

associated option byte, the WDGRF flag can not

be used in the application.

70

AVD

S

AVD

IE

AVD

F

LVD

RF

0

CSS

IE

CSS

D

WDG

RF

RESET Sources

LVDRF

WDGRF

External RESET pin

0

Watchdog

0

1

LVD

1

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST72521R7T5/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72521AR7TC/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72521M9T3/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP80 |

| ST72622K2B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72P621J4B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST72561K4 | 制造商:STMicroelectronics 功能描述:LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,FLASH MEMORY, - Bulk |

| ST72589-EMU2 | 功能描述:仿真器/模擬器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST72611F1 | 制造商:STMicroelectronics 功能描述:LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,FLASH MEMORY, - Bulk |

| ST7263-EMU2 | 功能描述:仿真器/模擬器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。