- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372394 > SX18ACDP IC-8-BIT MCU PDF資料下載

參數(shù)資料

| 型號(hào): | SX18ACDP |

| 英文描述: | IC-8-BIT MCU |

| 中文描述: | 集成電路8位微控制器 |

| 文件頁(yè)數(shù): | 30/42頁(yè) |

| 文件大小: | 312K |

| 代理商: | SX18ACDP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

1999 Scenix Semiconductor, Inc. All rights reserved.

- 30 -

www.scenix.com

SX18AC / SX20AC / SX28AC

15.13

Comparison and Conditional Branch

Instructions

The instruction set includes instructions such as DECSZ

fr (decrement file register and skip if zero), INCSZ fr

(increment file register and skip if zero), SNB bit (bit test

file register and skip if bit clear), and SB bit (bit test file

register and skip if bit set). These instructions will cause

the next instruction to be skipped if the tested condition is

true. If a skip instruction is immediately followed by a

PAGE or BANK instruction (and the tested condition is

true) then two instructions are skipped and the operation

consumes three cycles. This is useful for conditional

branching to another page where a PAGE instruction

precedes a JMP. If several PAGE and BANK instructions

immediately follow a skip instruction then they are all

skipped plus the next instruction and a cycle is consumed

for each.

15.14

Logical Instruction

The instruction set contain a full complement of the logi-

cal instructions (AND, OR, Exclusive OR), with the W

register and a selected memory location (using either

direct or indirect addressing) serving as the two oper-

ands.

15.15

Shift and Rotate Instructions

The instruction set includes instructions for left or right

rotate-through-carry.

15.16

Complement and SWAP

The device can perform one’s complement operation on

the file register (fr) and W register. The MOV W,<>fr

instruction performs nibble-swap on the fr and puts the

value into the W register.

15.17

Key to Abbreviations and Symbols

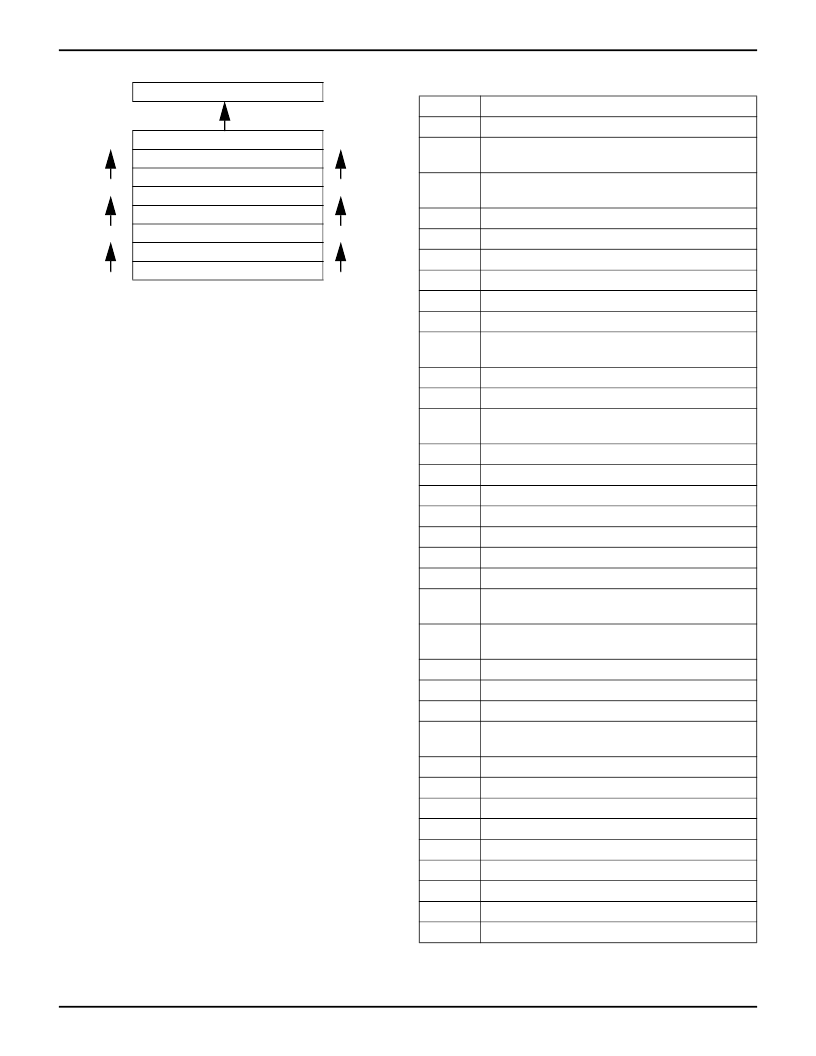

PC<10:0>

STACK 1

STACK 2

STACK 3

STACK 4

STACK 5

STACK 6

STACK 7

STACK 8

Symbol

W

fr

Description

Working register

File register (memory-mapped register in the

range of 00h to FFh)

Lower eight bits of program counter (file regis-

ter 02h)

STATUS STATUS register (file register 03h)

FSR

File Select Register (file register 04h)

C

Carry bit in STATUS register (bit 0)

DC

Digit Carry bit in STATUS register (bit 1)

Z

Zero bit in STATUS register (bit 2

PD

Power Down bit in STATUS register (bit 3)

TO

Watchdog Timeout bit in STATUS register (bit

4)

PA2:PA0 Page select bits in STATUS register (bits 7:5)

OPTION OPTION register (not memory-mapped)

WDT

Watchdog Timer register (not memory-

mapped)

MODE

MODE register (not memory-mapped)

rx

Port control register pointer (RA, RB, or RC)

!

Non-memory-mapped register designator

f

File register address bit in opcode

k

Constant value bit in opcode

n

Numerical value bit in opcode

b

Bit position selector bit in opcode

.

File register / bit selector separator in assem-

bly language instruction

#

Immediate literal designator in assembly lan-

guage instruction

lit

Literal value in assembly language instruction

addr8

8-bit address in assembly language instruction

addr9

9-bit address in assembly language instruction

addr12

12-bit address in assembly language instruc-

tion

/

Logical 1’s complement

|

Logical OR

^

Logical exclusive OR

&

Logical AND

<>

Swap high and low nibbles (4-bit segments)

<<

Rotate left through carry bit

>>

Rotate right through carry bit

- -

Decrement file register

++

Increment file register

PC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SX18ACSO | IC-SM-8 BIT MCU |

| SX20AC100SO | IC-SM-8-BIT MCU |

| SXA-1 | Amplifier. Other |

| SXA-2 | Amplifier. Other |

| SXA-3 | Amplifier. Other |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SX18ACSO | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:IC-SM-8 BIT MCU |

| SX18AD100-I/DP | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX18AD100-I/PQ | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX18AD100-I/SO | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX18AD100-I/SS | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。