- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383868 > SY89295U (Micrel Semiconductor,Inc.) 2.5V / 3.3V 1.5 GHZ PRECISION LVPECL PROGRAMMABLE DELAY PDF資料下載

參數(shù)資料

| 型號: | SY89295U |

| 廠商: | Micrel Semiconductor,Inc. |

| 英文描述: | 2.5V / 3.3V 1.5 GHZ PRECISION LVPECL PROGRAMMABLE DELAY |

| 中文描述: | 為2.5V / 3.3V的1.5 GHz的精密可編程延遲的LVPECL |

| 文件頁數(shù): | 4/15頁 |

| 文件大?。?/td> | 169K |

| 代理商: | SY89295U |

4

Precision Edge

SY89295U

Micrel

M9999-031604

hbwhelp@micrel.com or (408) 955-1690

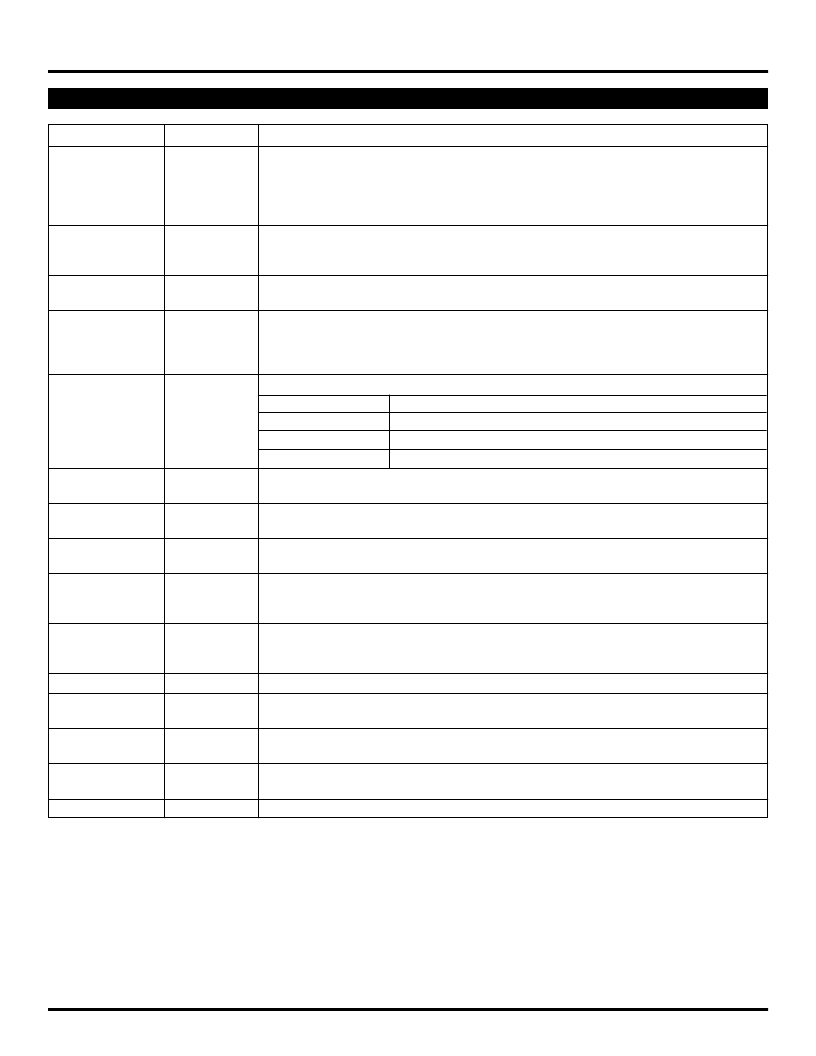

Pin Number

Pin Name

Pin Function

23, 25, 26, 27, 29,

30, 31, 32, 1, 2

D[9:0]

CMOS, ECL, or TTL Control Bits: These control signals adjust the delay from IN to Q.

See

“

AC Electrical Characteristics

”

for delay values. In addition, see

“

Interface Applications

”

section which illustrates the proper interfacing techniques for different logic standards.

D[9:0] contains pull-downs and defaults LOW when left floating. D0 (LSB), and D9 (MSB).

See

“

Typical Operating Characteristics

”

for delay information.

3

D10

CMOS, ECL, or TTL Control Bit: This bit is used to cascade devices for an extended delay

range. In addition, it drives CASCADE, and /CASCADE. Further, D[10] contains a pull-

down and defaults LOW when left floating.

LVPECL/ECL Signal Input: Input signal to be delayed. IN contains a 75k

pull-down and

will default to a logic LOW if left floating.

4, 5

IN, /IN

6

VBB

(1)

Reference Voltage Output: When using a single-ended input signal source to IN or /IN,

connect the unused input of the differential pair to this pin. This pin can also be used to

rebias AC-coupled inputs to IN and /IN. When used, de-couple to V

CC

using a 0.01

μ

F

capacitor, otherwise leave floating if not used. Maximum sink/source is

±

0.5mA.

Reference Voltage Output: Connect this pin to V

CF

when D[9:0], and D[10] is ECL.

Logic Standard

V

CF

Connects to

LVPECL

V

EF

,

(1)

CMOS

No Connect

TTL

1.5V Source

7

VEF

8

VCF

Reference Voltage Input: The voltage driven on V

CF

sets the logic transition threshold for

D[9:0], and D[10].

9, 24, 28

GND,

Negative Supply: For MLF

package, exposed pad must be connected to a ground plane

that is the same potential as the ground pin.

Exposed Pad

(2)

10

LEN

ECL Control Input: When HIGH latches the D[9:0] and D[10] bits. When LOW, the D[9:0]

and D[10] latches are transparent.

11

SETMIN

ECL Control Input: When HIGH, D[9:0] registers are reset. When LOW, the delay is set

by SETMAX or D[9:0] and D[10]. SETMIN contains a pull-down and defaults LOW when

left floating.

12

SETMAX

ECL Control Input: When SETMAX is set HIGH and SETMIN is set LOW, D[9:0] =

10

’

b1111111111. When SETMAX is LOW, the delay is set by SETMIN or D[9:0] and

D[10]. SETMAX contains a pull-down and defaults LOW when left floating.

Positive Power Supply: Bypass with 0.1

μ

F and 0.01

μ

F low ESR capacitors.

LVPECL Differential Output: The outputs are used when cascading two or more

SY89295U to extend the delay range.

13, 18, 19, 22

VCC

14, 15

/Cascade,

Cascade

16

/EN

LVPECL Single-Ended Control Input: When LOW, Q is delayed from IN. When HIGH,

Q is a differential LOW. /EN contains a pull-down and defaults LOW when left floating.

20, 21

/Q, Q

LVPECL Differential Output: Q is a delayed version of IN. Always terminate the

output with 50

to V

CC

–

2V. See

“

Output Interface Applications

”

section.

No Connect.

17

NC

Notes:

1. Single-ended operation is only functional at 3.3V.

2. MLF

package only.

PIN DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| SY89306 | 3.3V / 5V 2.5 GHZ PECL/ECL DIFFERENTIAL RECEIVER/BUFFER |

| SY89306V | 3.3V / 5V 2.5 GHZ PECL/ECL DIFFERENTIAL RECEIVER/BUFFER |

| SY89306VMGTR | 3.3V / 5V 2.5 GHZ PECL/ECL DIFFERENTIAL RECEIVER/BUFFER |

| SY89316V | 3.3V / 5V 2.5 GHZ PECL/ECL DIFFERENTIAL RECEIVER/BUFFER |

| SY89316VMGTR | 3.3V / 5V 2.5 GHZ PECL/ECL DIFFERENTIAL RECEIVER/BUFFER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SY89295U_06 | 制造商:MICREL 制造商全稱:Micrel Semiconductor 功能描述:2.5V/3.3V 1.5GHz PRECISION LVPECL PROGRAMMABLE DELAY |

| SY89295U_11 | 制造商:MICREL 制造商全稱:Micrel Semiconductor 功能描述:2.5V/3.3V 1.5GHz Precision LVPECL |

| SY89295U-EVAL | 制造商:Micrel Inc 功能描述:2.5V/3.3V PECL DELAY LINE - EV |

| SY89295UMG | 功能描述:延遲線/計時元素 2.5V/3.3V PECL Delay Line (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 傳播延遲時間:1000 ps 工作溫度范圍: 封裝 / 箱體:QFN-24 封裝:Tube |

| SY89295UMG TR | 功能描述:延遲線/計時元素 2.5V/3.3V PECL Delay Line (I Temp, Green) RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 傳播延遲時間:1000 ps 工作溫度范圍: 封裝 / 箱體:QFN-24 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。