- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄272328 > T80C31-20D (ATMEL CORP) 8-BIT, 20 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | T80C31-20D |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 20 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | 1 MM HEIGHT, QFP-44 |

| 文件頁數(shù): | 93/170頁 |

| 文件大小: | 4133K |

| 代理商: | T80C31-20D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁

29

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

When VLM is active and voltage at V

CC is above the selected trigger level operation will be as normal and the VLM

can be shut down for a short period of time. If voltage at V

CC drops below the selected threshold the VLM will either

flag an interrupt or generate a reset, depending on the configuration.

When the VLM has been configured to generate a reset at low supply voltage it will keep the device in reset as long

as V

CC is below the reset level. See Table 8-4 on page 34 for reset level details. If supply voltage rises above the

reset level the condition is removed and the MCU will come out of reset, and initiate the power-up start-up

sequence.

If supply voltage drops enough to trigger the POR then PORF is set after supply voltage has been restored.

8.2.3

External Reset

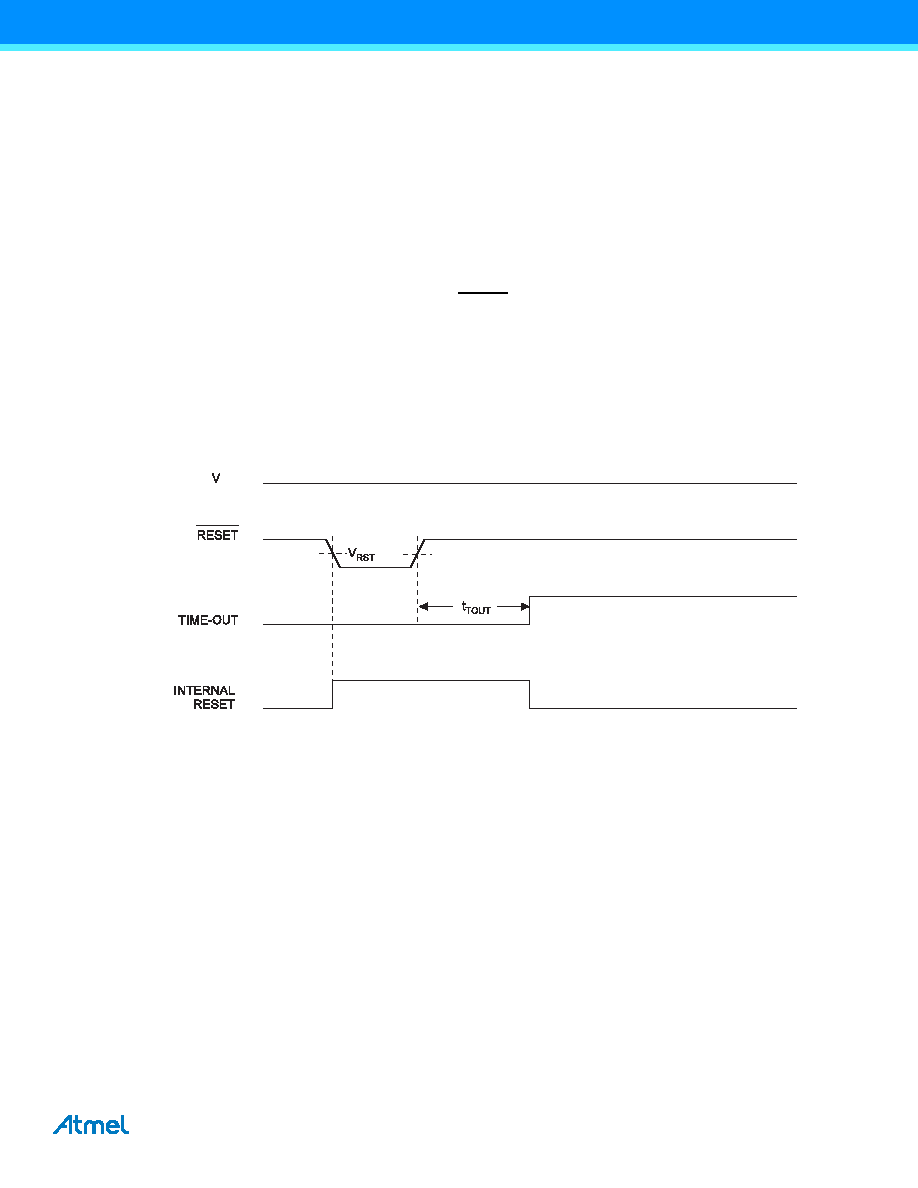

An External Reset is generated by a low level on the RESET pin if enabled. Reset pulses longer than the minimum

pulse width (see section “System and Reset Characteristics” on page 118) will generate a reset, even if the clock is

not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset

Threshold Voltage – V

RST – on its positive edge, the delay counter starts the MCU after the time-out period – tTOUT

– has expired. External reset is ignored during Power-on start-up count. After Power-on reset the internal reset is

extended only if RESET pin is low when the initial Power-on delay count is complete. See Figure 8-2 and Figure 8-

Figure 8-4.

External Reset During Operation

8.2.4

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of

this pulse, the delay timer starts counting the time-out period t

TOUT. See page 30 for details on operation of the

Watchdog Timer and Table 16-4 on page 118 for details on reset time-out.

CC

相關PDF資料 |

PDF描述 |

|---|---|

| TSC87C52-25MIMQ | 8-BIT, OTPROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| TSC87C52-25MJ | 8-BIT, UVPROM, 25 MHz, MICROCONTROLLER, CDIP40 |

| TSC87C52-25MK/883 | 8-BIT, UVPROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| TMP87CH00DF | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| T80C31U-L:D | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| T80C31-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| T80C31-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| T80C31-36 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| T80C31-40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| T80C31-42 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。