- 您現在的位置:買賣IC網 > PDF目錄361357 > T81L0006B-BD (TM Technology, Inc.) 8-bit A/D Type MCU PDF資料下載

參數資料

TE

CH

tm

mode 1 and 3. RCLK=0 causes timer1 overflow to be used for the receive clock

T2CON.4: TCLK Transmit clock flag. When set, cause the serial port to use timer2 overflow pulses for its transmit clock in

mode 1 and 3. TCLK=0 causes timer1 overflow to be used for the transmit clock

T2CON.3: EXEN2 Timer2 external enable flag. When set, allows a capture or reload to occur as a result of a negative

transition on T2EX if timer2 is not being used to clock the serial port. EXEN2=0 causes timer2 to ignore events at T2EX.

T2CON.2: Start/stop control for timer2. A logic 1 starts the timer

T2CON.1: Timer or counter select. (Timer 2) , 0 as internal timer

T2CON.0: Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN2=1. When cleared,

auto reloads will occur either with timer2 overflow or negative transitions at T2EX when EXEN2=1. When either RCLK=1

or TCLK=1, this bit is ignored and the timer is forced to auto-reload on timer2 overflow.

Note then the baudrates for transmit and receive can be simultaneously different. Setting RCLK and/or TCLK puts Timer2

into its baudrate generator mode.

The baudrate generator mode is similar to the auto reload mode, in that a rollover is TH2 causes the Timer2 registers to be

reload with the 16 bit value in registers RCAP2H and RCAP2L, which are preset by software given by the formula.

Baudrate= (Timer2 overflow rate)/16 =(Oscillator Frequency) / (32*(65536-(RCAP2H,RCAP2L)))

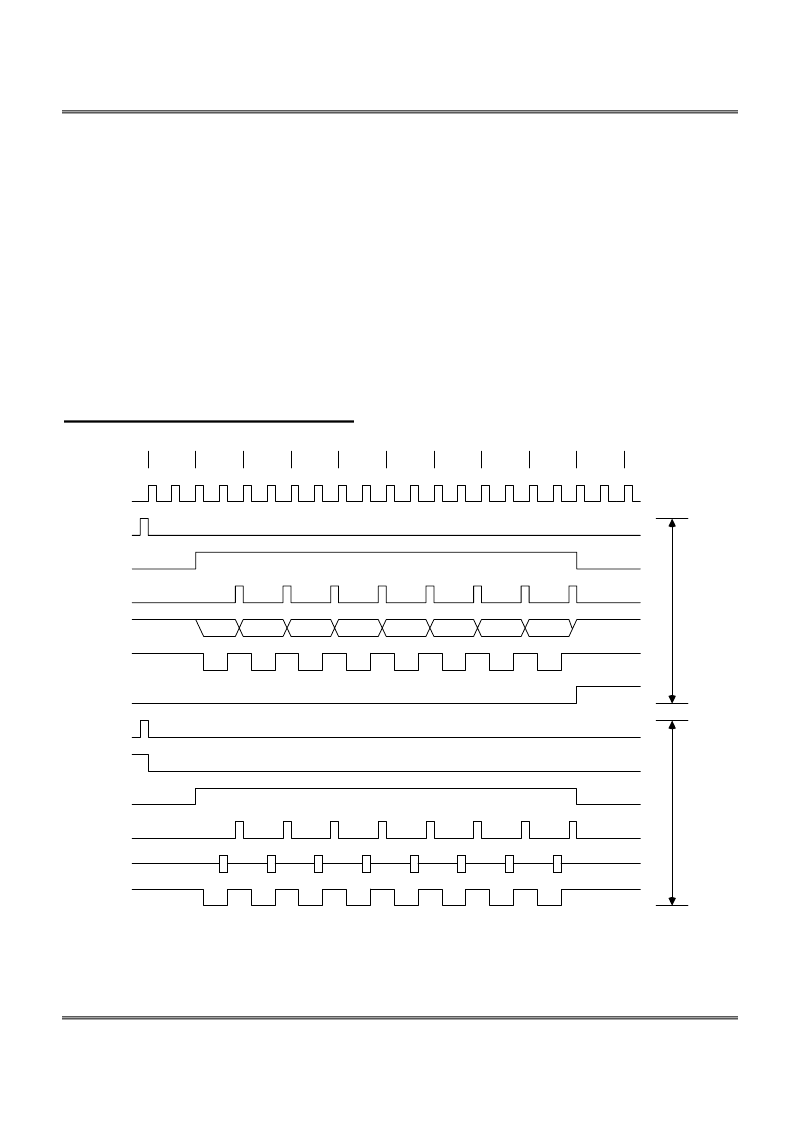

Serial Interface Timing Diagram

T81L0006A/B

TM Technology Inc. reserves the right

P. 10

Publication Date: AUG. 2005

to change products or specifications without notice. Revsion : B

S1.........S6 S1.........S6

S1.........S6

S1.........S6

S1.........S6 S1.........S6

S1.........S6 S1.........S6

S1.........S6

S1.........S6

ALE

D0

D1

D2

D3

D4

D5

D6

D7

RXD

TXD

D0

D1

D2

D3

D4

D5

D6

D7

RXD

TXD

Receive

Shift

Write to SCON, Clear RI

RI

Write to SBUF

Send

Shift

Serial Port Mode 0

相關PDF資料 |

PDF描述 |

|---|---|

| T81L0006B-BK | 8-bit A/D Type MCU |

| T81L0006A-AK | 8-bit A/D Type MCU |

| T81L0006A-BD | 8-bit A/D Type MCU |

| T81L0006A-BK | 8-bit A/D Type MCU |

| T81L0006A-CD | 8-bit A/D Type MCU |

相關代理商/技術參數 |

參數描述 |

|---|---|

| T81L0006B-BK | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit A/D Type MCU |

| T81L0010A | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit MCU |

| T81L0010A_06 | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit MCU |

| T81L0010A-AD | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit MCU |

| T81L0010A-AK | 制造商:TMT 制造商全稱:TMT 功能描述:8-bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復。