- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68120 > TC1303C-NH1EMFTR 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 PDF資料下載

參數(shù)資料

| 型號(hào): | TC1303C-NH1EMFTR |

| 元件分類(lèi): | 穩(wěn)壓器 |

| 英文描述: | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

| 封裝: | 3 X 3 MM, 0.9 MM HEIGHT, PLASTIC, DFN-10 |

| 文件頁(yè)數(shù): | 20/38頁(yè) |

| 文件大小: | 756K |

| 代理商: | TC1303C-NH1EMFTR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

2008 Microchip Technology Inc.

DS21949C-page 27

TC1303A/TC1303B/TC1303C/TC1304

As an example, for a 3.6V input, 1.8V output with a load

of 400 mA, the efficiency taken from Figure 2-8 is

approximately 84%. The internal power dissipation is

approximately 137 mW.

5.6.2

LDO OUTPUT (VOUT2)

The internal power dissipation within the TC1303/

TC1304 LDO is a function of input voltage, output

voltage and output current. Equation 5-7 can be used

to calculate the internal power dissipation for the LDO.

EQUATION 5-7:

The maximum power dissipation capability for a

package can be calculated given the junction-to-

ambient thermal resistance and the maximum ambient

temperature for the application. The following equation

can be used to determine the package’s maximum

internal power dissipation.

5.6.3

LDO POWER DISSIPATION

EXAMPLE

5.7

PCB Layout Information

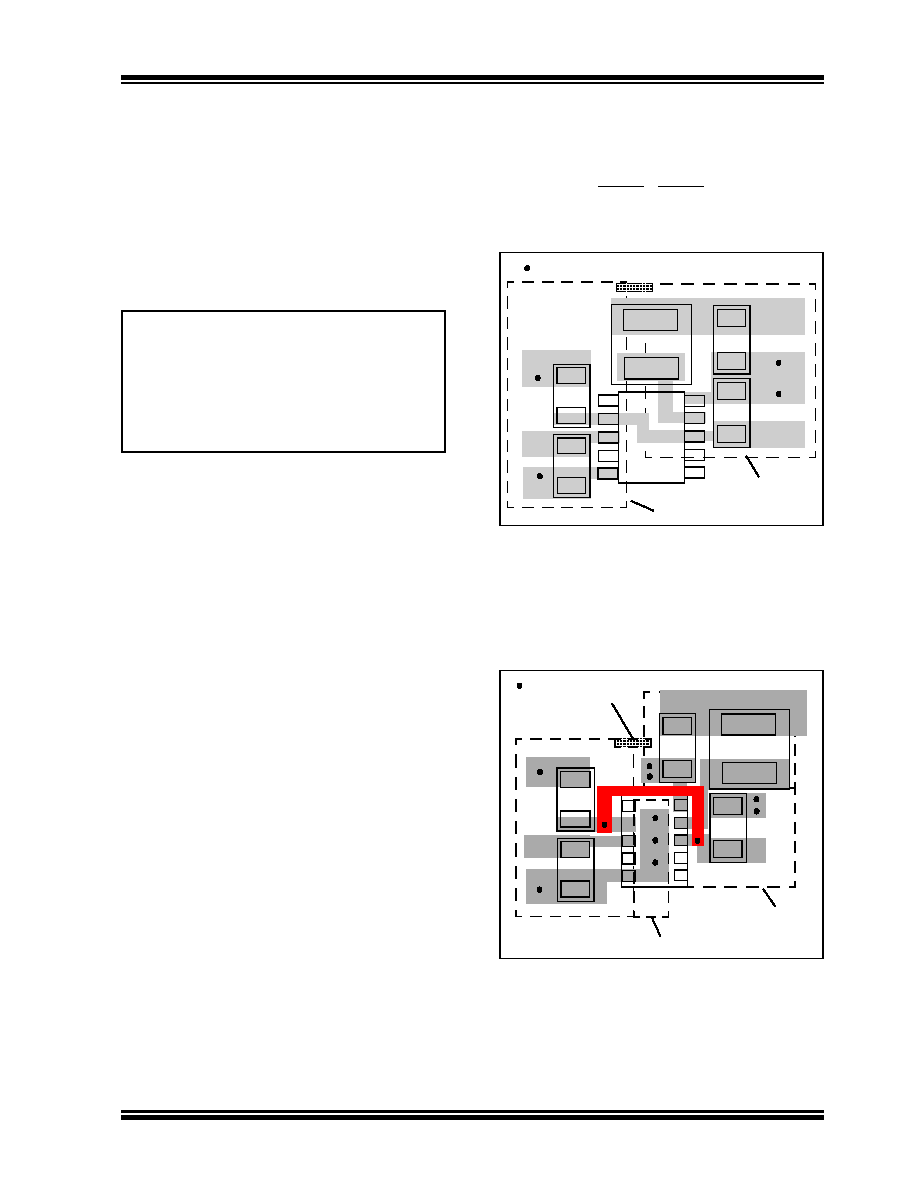

Some basic design guidelines should be used when

physically placing the TC1303/TC1304 on a Printed

Circuit Board (PCB). The TC1303/TC1304 has two

ground pins, identified as AGND (analog ground) and

PGND (power ground). By separating grounds, it is

possible to minimize the switching frequency noise on

the LDO output. The first priority, while placing external

components on the board, is the input capacitor (CIN1).

Wiring should be short and wide; the input current for

the TC1303/TC1304 can be as high as 800 mA. The

next priority would be the buck regulator output

capacitor (COUT1) and inductor (L1). All three of these

components are placed near their respective pins to

minimize trace length. The CIN1 and COUT1 capacitor

returns are connected closely together at the PGND

plane. The LDO optional input capacitor (CIN2) and

LDO output capacitor COUT2 are returned to the AGND

plane. The analog ground plane and power ground

plane are connected at one point (shown near L1). All

other signals (SHDN1, SHDN2, feedback in the

adjustable-output case) should be referenced to AGND

and have the AGND plane underneath them.

FIGURE 5-1:

Component Placement,

Fixed 10-Pin MSOP.

There will be some difference in layout for the 10-pin

DFN package due to the thermal pad. A typical fixed-

output DFN layout is shown below. For the DFN layout,

the VIN1 to VIN2 connection is routed on the bottom of

the board around the TC1303/TC1304 thermal pad.

FIGURE 5-2:

Component Placement,

Fixed 10-Pin DFN.

Input Voltage

VIN =5V±10%

LDO Output Voltage and Current

VOUT =3.3V

IOUT = 300 mA

Internal Power Dissipation

PLDO(MAX) =(VIN(MAX) – VOUT2(MIN)) x IOUT2(MAX)

PLDO = (5.5V – 0.975 x 3.3V) x 300 mA

PLDO = 684.8 mW

P

LDO

V

IN MAX

)

()

V

OUT2 MIN

()

–

() I

OUT2 MAX

)

()

×

=

Where:

PLDO = LDO Pass device internal power

dissipation

VIN(MAX) = Maximum input voltage

VOUT(MIN) = LDO minimum output voltage

TC1303B

1

2

6

8

7

9

10

5

4

3

+VOUT1

PGND

+VIN1

AGND

+VOUT2

COUT1

CIN2

COUT2

CIN1

PGND Plane

AGND Plane

L1

AGND to PGND

+VIN2

* CIN2 Optional

-

Via

1

2

6

8

7

9

10

5

4

3

+VOUT1

PGND

+VIN1

AGND

+VOUT2

COUT1

CIN2

COUT2

CIN1

PGND Plane

AGND Plane

L1

AGND to PGND

PGND

* CIN2 Optional

+VIN2

TC1303B

- Via

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TC1303C-NI0EMFTR | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

| TC1303C-NK0EMF | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

| TC1303C-NM3EUNTR | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

| TC1303C-OA1EUN | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

| TC1303C-OB3EMF | 0.5 A SWITCHING REGULATOR, 2400 kHz SWITCHING FREQ-MAX, PDSO10 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TC1303C-PA0EMF | 功能描述:低壓差穩(wěn)壓器 - LDO PWM LDO combo PG RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| TC1303C-PA0EMFTR | 功能描述:低壓差穩(wěn)壓器 - LDO PWM LDO combo PG RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| TC1303C-PC0EMF | 功能描述:低壓差穩(wěn)壓器 - LDO PWM LDO combo PG RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| TC1303C-PI0EMF | 功能描述:低壓差穩(wěn)壓器 - LDO PWM/LDO combo w/PG RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| TC1303C-PI0EMFTR | 功能描述:低壓差穩(wěn)壓器 - LDO PWM/LDO combo w/PG RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。