- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > TDA10045H (NXP SEMICONDUCTORS) DVB-T channel receiver PDF資料下載

參數(shù)資料

| 型號: | TDA10045H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | DVB-T channel receiver |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | 14 X 20 X 2.80 MM, PLASTIC, QFP-100 |

| 文件頁數(shù): | 6/20頁 |

| 文件大?。?/td> | 94K |

| 代理商: | TDA10045H |

2001 Nov 08

6

Philips Semiconductors

Product specification

DVB-T channel receiver

TDA10045H

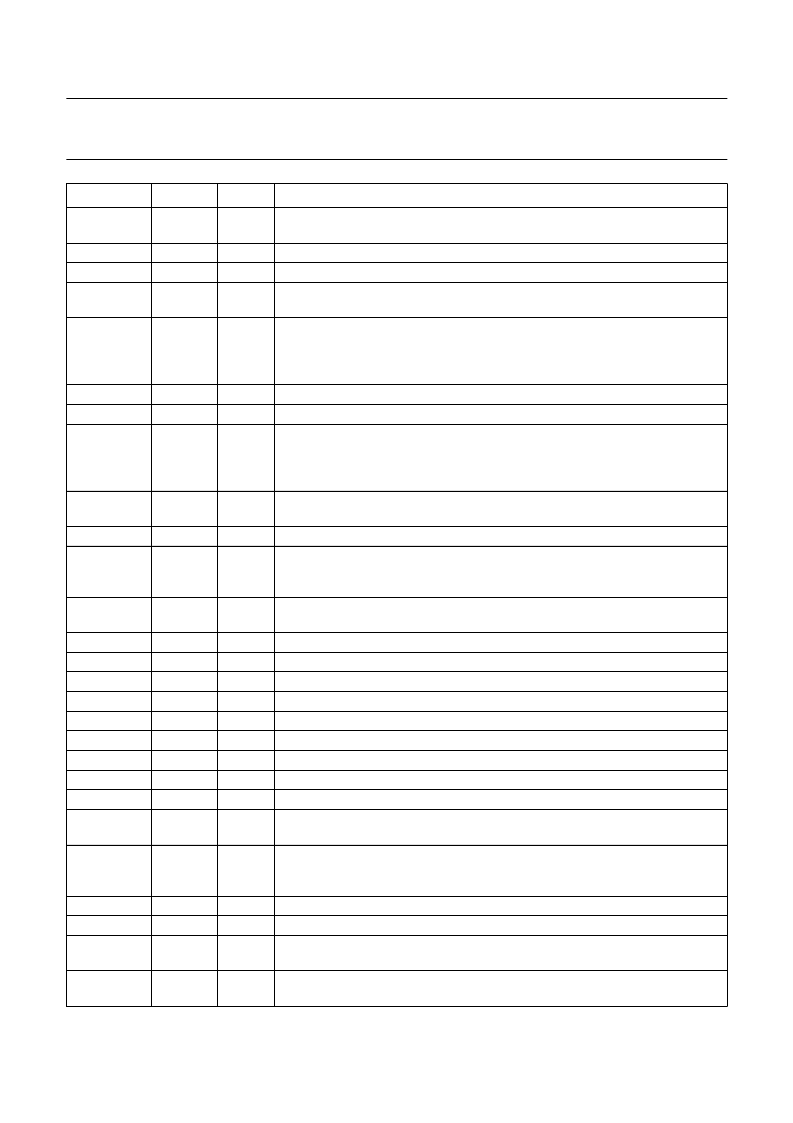

FFT_WIN

30

I/O

output or input signal indicating the start of the active data; equals 1 during

complex sample 0 of the active FFT block; can be used to synchronize 2 chips

digital supply voltage for the pads (3.3 V typ.)

digital ground supply (0 V)

sampling frequency output; this output clock can be fed to an external (10-bit)

ADC as a sampling clock; SACLK can also provide twice the sampling clock

input data from an external ADC, FI must be tied to ground when unused,

positive notation (from 0 to 1023) or twos complement notation (from

512 to +511). In internal ADC mode, these outputs can be used to monitor

extra demodulator output signals (constellation or frequency response).

digital supply voltage for the core (1.8 V typ.)

digital ground supply (0 V)

input data from an external ADC, FI must be tied to ground when unused,

positive notation (from 0 to 1023) or twos complement notation (from

512 to +511). In internal ADC mode, these outputs can be used to monitor

extra demodulator output signals (constellation or frequency response).

digital supply voltage (5 V typ.); can be set to 3.3 V (with caution) if 5 V tolerant

I/O is not required

digital ground supply (0 V)

interrupt line; this output interrupt line can be configured by the I

2

C-bus

interface. This pin is an open-drain output and therefore requires an external

pull-up resistor (to V

DDD33

or V

DDD50

).

front-end lock; FEL is an open-drain output and therefore requires an external

pull-up resistor (to V

DDD33

or V

DDD50

)

not connected

not connected

asynchronous reset signal for boundary scan; connected to GND if not used

mode programming signal for boundary scan; connected to GND if not used

input port for boundary scan; connected to GND if not used

clock signal for boundary scan; connected to GND if not used)

output port for boundary scan; not connected if not used

digital supply voltage for the core (1.8 V typ.)

digital ground supply (0 V)

spare delta-sigma output; managed by the DSP or by an I

2

C-bus register to

generate an analog level (after a RC low-pass filter)

spare delta-sigma output; managed by the DSP to handle a low frequency DAC

(automatic first stage tuner AGC measurement or 2nd AGC loop control as

examples)

digital supply voltage for the pads (3.3 V typ.)

digital ground supply (0 V)

RS error flag, active HIGH on one RS packet if the RS decoder fails to correct

the errors

pulse synchro; this output signal goes HIGH on a rising edge of OCLK when a

synchro byte is provided, then goes LOW until the next synchro byte

V

DDD33

V

SSD

SACLK

31

32

33

O

FI[9:5]

34 to 38

I/O

V

DDD18

V

SSD

FI[4:0]

39

40

IO

41 to 45

V

DDD50

46

V

SSD

IT

47

48

OD

(1)

FEL

49

OD

(1)

n.c.

n.c.

TRSTN

TMS

TDI

TCK

TDO

V

DDD18

V

SSD

DS_SPARE2

50

51

52

53

54

55

56

57

58

59

I

(2)

I

(2)

I

(2)

I

(2)

O

O

DS_SPARE1

60

O

V

DDD33

V

SSD

UNCOR

61

62

63

O

PSYNC

64

O

SYMBOL

PIN

TYPE

DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| TDA1005A | FREQUENCY MULTIPLEX PLL STEREO DECODER |

| TDA1005AT | FREQUENCY MULTIPLEX PLL STEREO DECODER |

| TDA10085 | Single chip DVB-S/DSS channel receiver |

| TDA10085HT | Single chip DVB-S/DSS channel receiver |

| TDA1010 | 6 W audio power amplifier in car applications 10 W audio power amplifier in mains-fed applications |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TDA10046AHT/C1,518 | 制造商:Trident Microsystems, Ltd. 功能描述:TTMTDA10046AHT/C1,518 HYBRID SILICON TUN |

| TDA10046HT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single-chip DVB-T channel |

| TDA10048HC/C200,557 | 制造商:NXP Semiconductors 功能描述:PHATDA10048HC/C200.557 REEL |

| TDA10048HN/C200,51 | 制造商:Entropic Communications 功能描述:TDA10048HN/HVQFN48/REEL13DP//C |

| TDA10048HN/C200,55 | 制造商:Entropic Communications 功能描述:TDA10048HN/HVQFN48/TRAYBDP//C2 |

發(fā)布緊急采購,3分鐘左右您將得到回復。