- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371182 > TDA8315 (NXP Semiconductors N.V.) Integrated NTSC decoder and sync processor PDF資料下載

參數(shù)資料

| 型號: | TDA8315 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Integrated NTSC decoder and sync processor |

| 中文描述: | 綜合NTSC制式解碼器和同步處理器 |

| 文件頁數(shù): | 11/16頁 |

| 文件大小: | 83K |

| 代理商: | TDA8315 |

September 1994

11

Philips Semiconductors

Preliminary specification

Integrated NTSC decoder

and sync processor

TDA8315T

13. The horizontal output pulses are obtained from the horizontal oscillator by a pulse shaper. The width of the output

pulse is approximately 5.4

μ

s and the rising edge of the pulse symmetrically coincides with the start of the sync pulse

at the input.

14. The vertical output pulses are generated by a divider circuit. The vertical output pulse has a delay of 37.5

μ

s with

respect to the start of the vertical sync pulse at the input. This is caused by the clock frequency of the divider being

twice the horizontal frequency.

This divider circuit has 2 modes of operation:

Search mode (large window).

This mode is switched on when the circuit is not synchronized or, when a non-standard signal is received (the number

of lines per frame outside the range is between 261 and 264). In the search mode the divider can be triggered

between line 244 and line 288 (approximately 54 to 64.5 Hz).

Standard mode (narrow window).

This mode is switched on when more than 15 successive vertical sync pulses are detected in the narrow window.

When the circuit is in the standard mode and a vertical sync pulse is missing the output pulse is generated at the end

of the window. Consequently, the disturbance of the picture is very small. The circuit will switch back to the search

window when, for 6 successive vertical periods, no sync pulses are found within the window. When no input signal

is available the divider generates output pulses with a timing of 262.5 lines (standard 60 Hz signal).

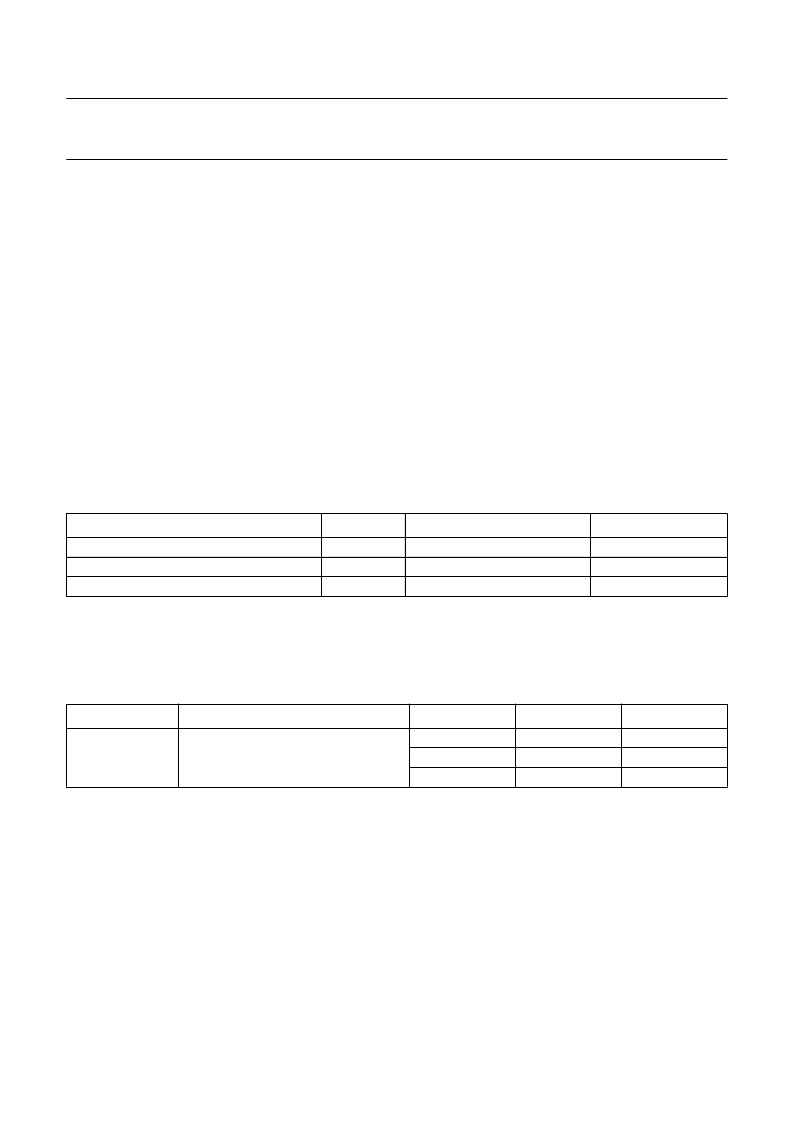

Table 1

Output current of phase detector.

Note

1.

Vertical retrace.

QUALITY SPECIFICATION

Quality level in accordance with SNW-FQ-611-part E.

Notes

1.

2.

3.

All pins are protected against ESD by means of internal clamping diodes.

Range A is for Human body model.

Range B is for machine model.

Latch up

All pins meet the specification:

I

trigger

≥

100 mA or

≥

1.5 V

DDmax

I

trigger

≤

100 mA or

≤

0.5 V

DDmax

.

CURRENT PHASE DETECTOR DURING

SCAN (

μ

A)

30

180

180

VERTICAL RETRACE (

μ

A)

GATED YES/NO

YES (5.7

μ

s)

YES (12

μ

s)

(1)

NO

Weak signal and synchronized

Strong signal and synchronized

Not synchronized

30

270

270

SYMBOL

PARAMETER

RANGE A

(2)

RANGE B

(3)

UNIT

ESD

protection circuit specification (note 1)

>2000

100

1500

>200

200

V

pF

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA8315T | Integrated NTSC decoder and sync processor |

| TDA8390 | PAL DECODER AND RGB MATRIX |

| TDA8405 | TV AND VTR STEREO/DUAL SOUND PROCESSOR WITH I2C BUS CONTROL |

| TDA844 | Cap |

| TDA8444 | Octuple 6-bit DACs with I2C-bus |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA8315T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated NTSC decoder and sync processor |

| TDA8315TD-G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TV/Video Sync Circuit |

| TDA8340 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Television IF amplifier and demodulator |

| TDA8341 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Television IF amplifier and demodulator |

| TDA8349 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multistandard IF amplifier and demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復。