- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25640 > MSP430F2003TRSAR (TEXAS INSTRUMENTS INC) 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 PDF資料下載

參數(shù)資料

| 型號(hào): | MSP430F2003TRSAR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 |

| 封裝: | GREEN, PLASTIC, QFN-16 |

| 文件頁(yè)數(shù): | 44/92頁(yè) |

| 文件大小: | 1672K |

| 代理商: | MSP430F2003TRSAR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

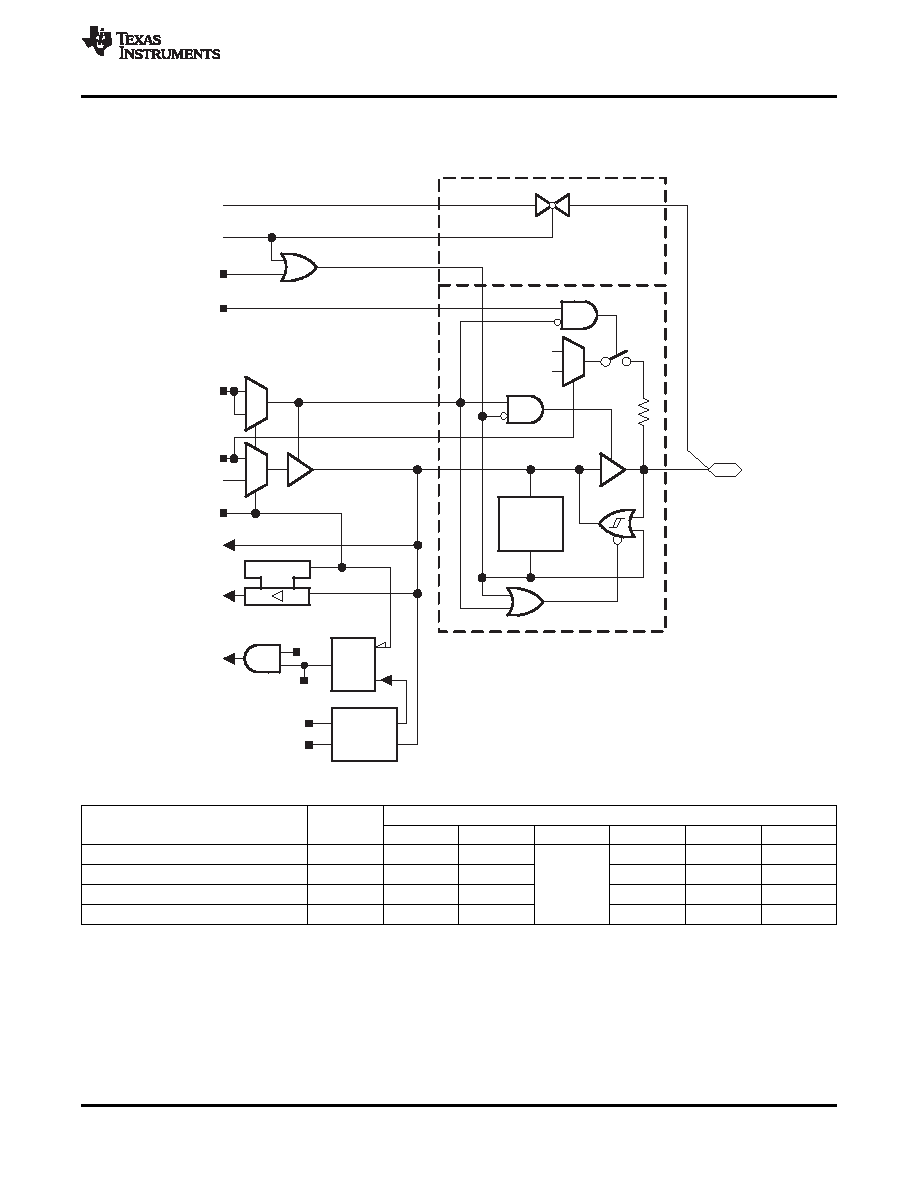

Bus

Keeper

EN

Direction

0: Input

1: Output

P1SEL.x

1

0

P1DIR.x

P1IN.x

P1IRQ.x

D

EN

Module X IN

1

0

Module X OUT

P1OUT.x

Interrupt

Edge

Select

Q

EN

Set

P1SEL.x

P1IES.x

P1IFG.x

P1IE.x

P1.0/TACLK/ACLK/CA0

P1.1/TA0/CA1

P1.2/TA1/CA2

P1.3/CAOUT/CA3

1

0

DVSS

DVCC

P1REN.x

CAPD.x

Pad Logic

From Comparator_A+

To Comparator_A+

1

MSP430F20x3

MSP430F20x2

MSP430F20x1

SLAS491H

– AUGUST 2005 – REVISED AUGUST 2011

APPLICATION INFORMATION, MSP430F20X1

Port P1 (P1.0 to P1.3) Pin Schematics, MSP430F20x1

Table 16. Control Signal

" From Comparator_A+"

SIGNAL "From Comparator_A+" = 1(1)

PIN NAME

FUNCTION

P2CA4

P2CA0

P2CA3

P2CA2

P2CA1

P1.0/TACLK/ACLK/CA0

CA0

0

1

N/A

P1.1/TA0/CA1

CA1

1

0

1

OR

P1.2/TA1/CA2

CA2

1

0

1

0

P1.3/CAOUT/CA3

CA3

N/A

0

1

(1)

N/A = Not available or not applicable

Copyright

2005–2011, Texas Instruments Incorporated

49

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP430F2012IRSAR | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 |

| MSP430F2013TRSAR | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 |

| MSP430F2001IRSA | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 |

| MSP430F2013IPWR | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PDSO14 |

| MSP430F2002IRSA | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSP430F2003TRSAT | 功能描述:16位微控制器 - MCU 16-Bit Ultra Low Pwr 1kB Flash 128B RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430F2011 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLER |

| MSP430F2011IN | 功能描述:16位微控制器 - MCU 16-Bit Ultra Low Pwr 1kB Flash 2kB RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430F2011IPW | 功能描述:16位微控制器 - MCU 16-Bit Ultra Low Pwr 1kB Flash 2kB RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430F2011IPWR | 功能描述:16位微控制器 - MCU 16-Bit Ultra Low Pwr 1kB Flash 2kB RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。