- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98235 > TLC1542QDWREP (TEXAS INSTRUMENTS INC) 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | TLC1542QDWREP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 11-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | GREEN, PLASTIC, SOIC-20 |

| 文件頁(yè)數(shù): | 24/25頁(yè) |

| 文件大?。?/td> | 573K |

| 代理商: | TLC1542QDWREP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)

TLC1542EP, TLC1543EP

10BIT ANALOGTODIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SGLS152A JANUARY 2004 REVISED FEBRUARY 2006

8

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

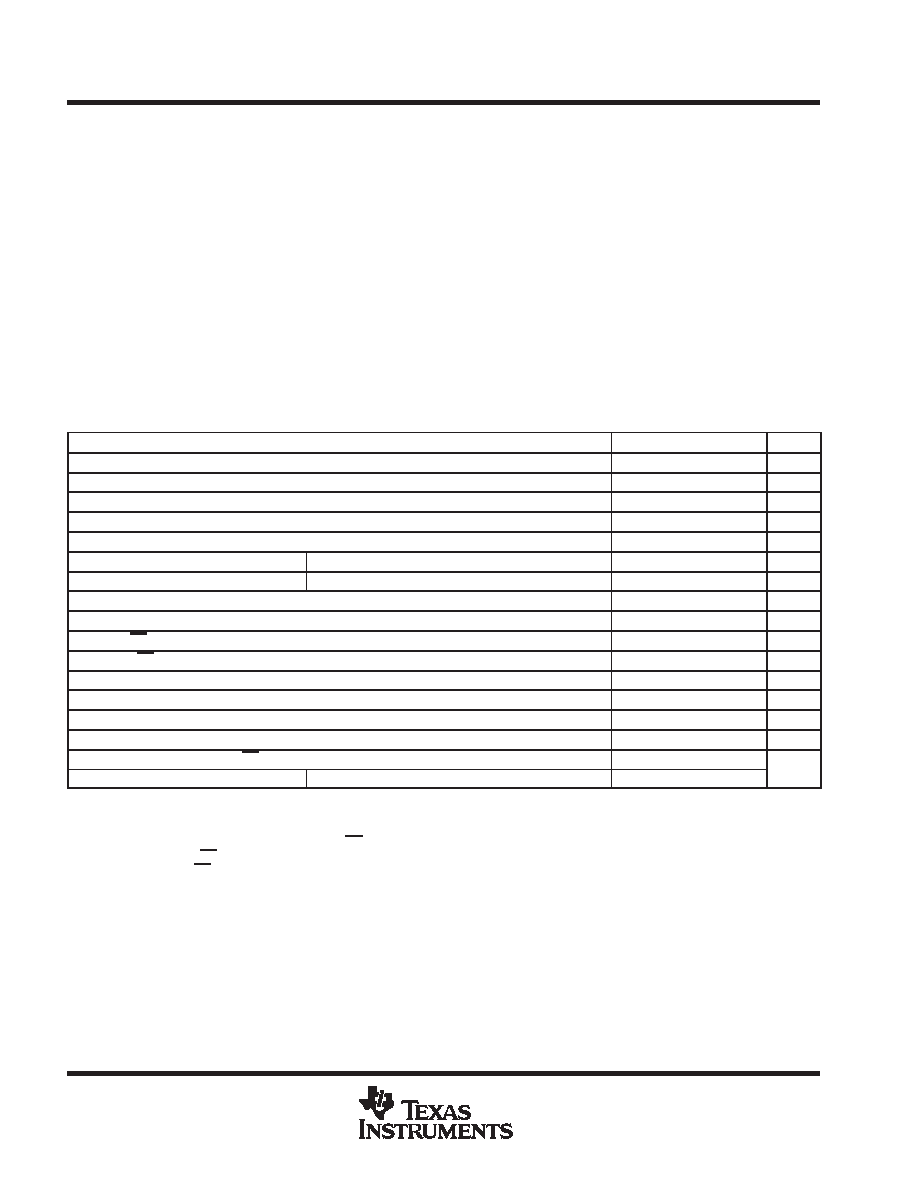

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC (see Note 1)

0.5 V to 6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI

0.3 V to VCC + 0.3 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, VO

0.3 V to VCC + 0.3 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Positive reference voltage, Vref+

VCC + 0.1 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Negative reference voltage, Vref

0.1 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak input current (any input)

±20 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak total input current (all inputs)

±30 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, TA

40

°C to 125°C

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, Tstg

65

°C to 150°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds

260

°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to digital ground with REF and GND wired together (unless otherwise noted).

recommended operating conditions

MIN

NOM

MAX

UNIT

Supply voltage, VCC

4.5

5

5.5

V

Positive reference voltage, Vref + (see Note 2)

VCC

V

Negative reference voltage, Vref (see Note 2)

0

V

Differential reference voltage, Vref + Vref (see Note 2)

2.5

VCC VCC + 0.2

V

Analog input voltage (see Note 2)

0

VCC

V

High-level control input voltage, VIH

VCC = 4.5 V to 5.5 V

2

V

Low-level control input voltage, VIL

VCC = 4.5 V to 5.5 V

0.8

V

Setup time, address bits at data input before I/O CLOCK

↑, tsu(A) (see Figure 4)

100

ns

Hold time, address bits after I/O CLOCK

↑, th(A) (see Figure 4)

0

ns

Hold time, CS low after last I/O CLOCK

↓, th(CS) (see Figure 5)

0

ns

Setup time, CS low before clocking in first address bit, tsu(CS) (see Note 3 and Figure 5)

1.425

s

Clock frequency at I/O CLOCK (see Note 4)

0

2.1

MHz

Pulse duration, I/O CLOCK high, twH(I/O)

190

ns

Pulse duration, I/O CLOCK low, twL(I/O)

190

ns

Transition time, I/O CLOCK, tt(I/O) (see Note 5 and Figure 6)

1

s

Transition time, ADDRESS and CS, tt(CS)

10

s

Operating free-air temperature, TA

TLC1542-EP, TLC1543-EP

40

125

°C

NOTES:

2. Analog input voltages greater than that applied to REF+ convert as all ones (1111111111), while input voltages less than that applied

to REF convert as all zeros (0000000000). The device is functional with reference voltages down to 1 V (Vref + Vref ); however,

the electrical specifications are no longer applicable.

3. To minimize errors caused by noise at CS, the internal circuitry waits for a setup time plus two falling edges of the internal system

clock after CS

↓ before responding to control input signals. Therefore, no attempt should be made to clock in an address until the

minimum CS setup time has elapsed.

4. For 11- to 16-bit transfers, after the tenth I/O CLOCK falling edge (

≤ 2 V) at least 1 I/O CLOCK rising edge (≥ 2 V) must occur within

9.5

s.

5. This is the time required for the clock input signal to fall from VIHmin to VILmax or to rise from VILmax to VIHmin. In the vicinity of

normal room temperature, the devices function with input clock transition time as slow as 1

s for remote data-acquisition

applications where the sensor and the A/D converter are placed several feet away from the controlling microprocessor.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC1549MJG | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP8 |

| TLC1549CP | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP8 |

| TLC1549IP | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP8 |

| TLC1549ID | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC1549IDG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC1542QFN | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit 11Chl A/D RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLC1542QN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 11 ANALOG INPUTS |

| TLC1543 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 11 ANALOG INPUTS |

| TLC1543C | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 11 ANALOG INPUTS |

| TLC1543CDB | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Hi-Spd A/D Conv RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。