TLC2551, TLC2552, TLC2555

5-V, LOW-POWER, 12-BIT, 175/360 KSPS,

SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS276D – MARCH 2000 – REVISED MAY 2003

6

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

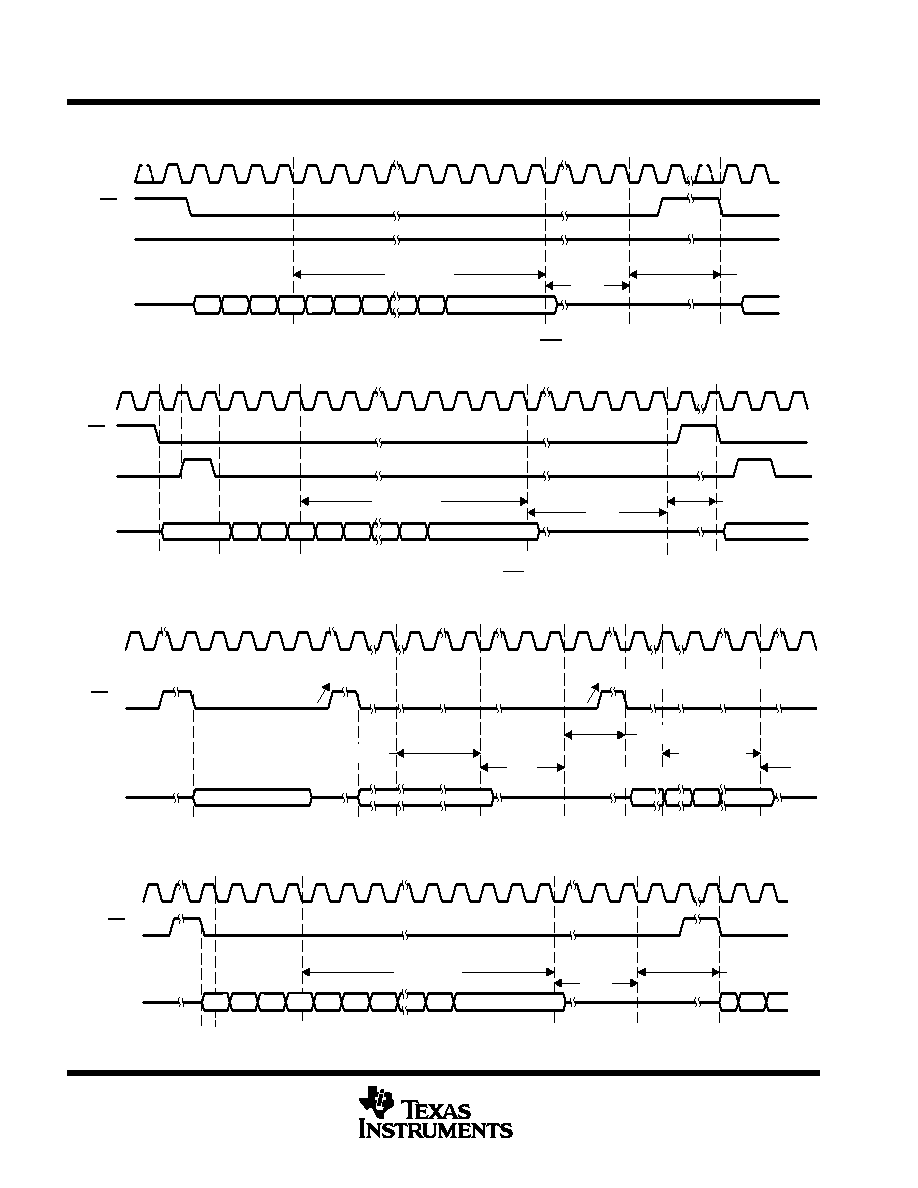

timing diagrams/conversion cycles

SCLK

1

2

3

4

5

6

12

13

14

15

16

1

CS

FS

OD8

OD7

OD6

OD5

OD0

SDO

t(sample)

tc

t(powerdown)

7

OD10

OD11

OD9

44

Figure 2. TLC2551 Timing: Control via CS (FS = 1)

SCLK

1

2

3

4

5

6

12

13

14

15

16

1

CS

FS

OD9

OD8

OD11

OD10

OD7

OD6

OD0

SDO

t(sample)

tc

t(powerdown)

44

Figure 3. TLC2551 Timing: Control via CS and FS or FS Only

SCLK

2

3

4

5

1

12

16

CS

SDO

t(powerdown)

tc

1

4

16

12

4

1

OD11

OD0

t(sample)

>8 SCLKs, MUX Toggles to AIN1

AIN0 Result

tc

<8 SCLKs, MUX

Resets to AIN0

t(sample)

44

Figure 4. TLC2552 Reset Timing

OD8

SCLK

1

2

3

4

5

6

12

13

14

15

16

CS

OD7

OD6

OD5

OD0

SDO

t(sample)

tc

t(powerdown)

7

OD9

1

OD10

OD9

OD11

OD10

OD11

44

Figure 5. TLC2552 and TLC2555 Timing