- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98249 > TLV1562CPWR (TEXAS INSTRUMENTS INC) 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV1562CPWR |

| 廠(chǎng)商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | ADC |

| 英文描述: | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | 0.65 MM PITCH, GREEN, TSSOP-28 |

| 文件頁(yè)數(shù): | 3/41頁(yè) |

| 文件大?。?/td> | 600K |

| 代理商: | TLV1562CPWR |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

TLV1562

2.7 V TO 5.5 V, HIGH-SPEED LOW-POWER RECONFIGURABLE ANALOG-TO-DIGITAL

CONVERTER WITH 4-INPUT, DUAL S/H, PARALLEL INTERFACE, AND POWER DOWN

SLAS162 – SEPTEMBER 1998

11

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

sampling/conversion

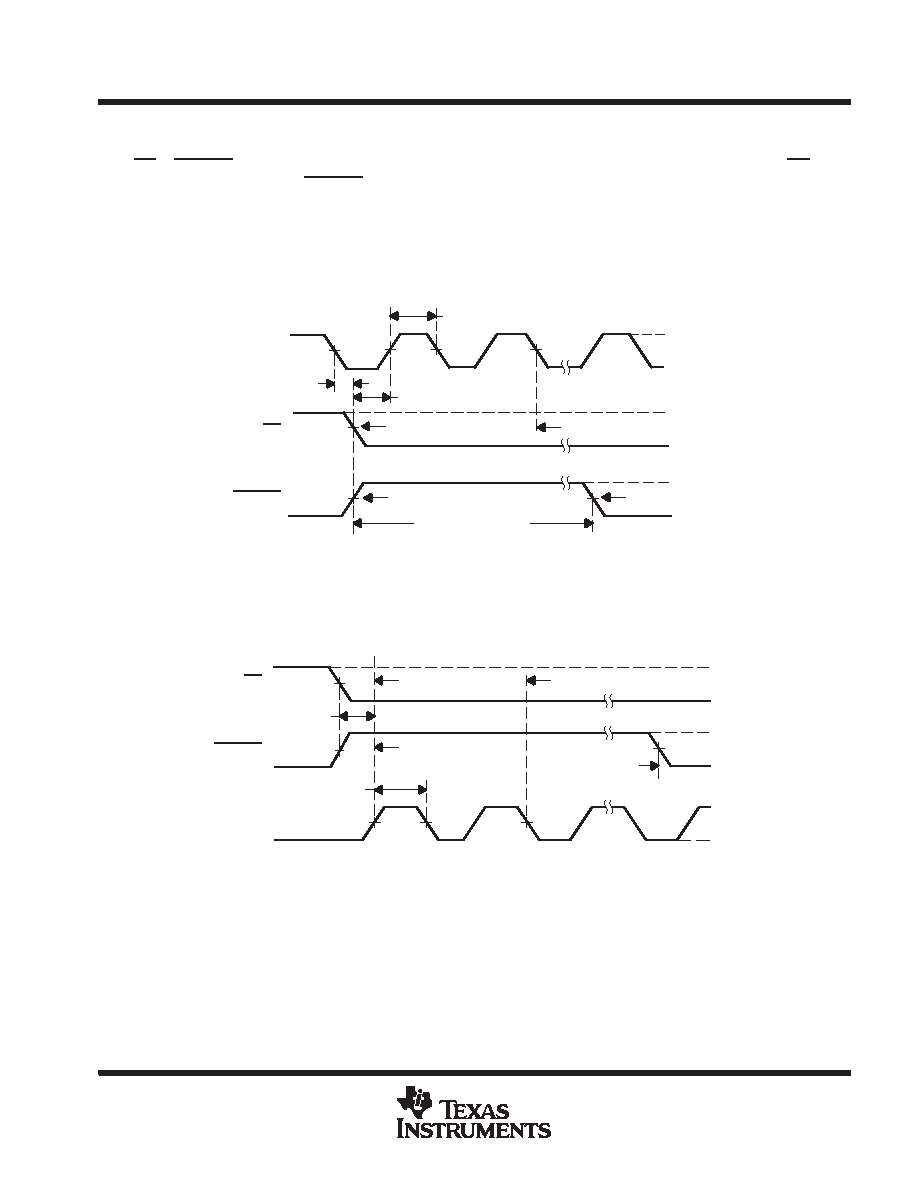

All of the sampling, conversion, and data output in the device are started by a trigger. This trigger can be the

RD or CSTART signal depending on the mode of conversion and configuration. The falling edge of the RD signal

and the rising edge of the CSTART signal are extremely important since they are used to start the conversion.

These edges need to stay as close to the falling edges of the external clock, if they are used as SYSCLK. The

minimum setup time with respect to the rising edge of the external SYSCLK should be 5 ns minimum. When

the internal SYSCLK is used, this is not an issue, since these two edges start the internal clock automatically;

therefore, the setup time is always met.

USING EXTERNAL CLOCK

S/H Hold Time

ts(TRGL-ECLKH)

Conversion Starts

Next Sampling Starts

td(ECLKL-TRGL)

Conversion Starts

Next Sampling Starts

Sampling Period

VIH

VIL

VIH

VIL

VIH

VIL

EXTERNAL

SYSCLK

RD

CSTART

Figure 8. Conversion Trigger Timing – External Clock

USING INTERNAL CLOCK

td(TRGL-ICLKH)

S/H Hold Time

Conversion Starts

Next Sampling

Starts

Conversion Starts

Next Sampling Starts

VIH

VIL

VIH

VIL

VIH

VIL

RD

CSTART

INTERNAL

SYSCLK

INTERNAL

CLOCK STARTS

Figure 9. Conversion Trigger Timing – Internal Clock

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV1562CPW | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562IPWR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562IPW | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562CPWG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562IDWG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV1562EVM | 制造商:Rochester Electronics LLC 功能描述:10- BIT A-D CONVERTER EVALUATION MODULE - Bulk 制造商:Texas Instruments 功能描述:10- BIT A-D CONVERTER EVALUATION MODULE - Bulk |

| TLV1562IDW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit Programmable RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IDWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IDWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IDWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。