- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV2548MFK (TEXAS INSTRUMENTS INC) 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC20 PDF資料下載

參數(shù)資料

| 型號: | TLV2548MFK |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC20 |

| 封裝: | CERAMIC, LCC-20 |

| 文件頁數(shù): | 14/39頁 |

| 文件大小: | 827K |

| 代理商: | TLV2548MFK |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

TLV2544Q, TLV2548Q, TLV2548M

3V TO 5.5V, 12BIT, 200KSPS, 4/8CHANNEL, LOW POWER

SERIAL ANALOGTODIGITAL CONVERTERS WITH AUTOPOWERDOWN

SGLS119F FEBRUARY 2002 REVISED OCTOBER 2009

21

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

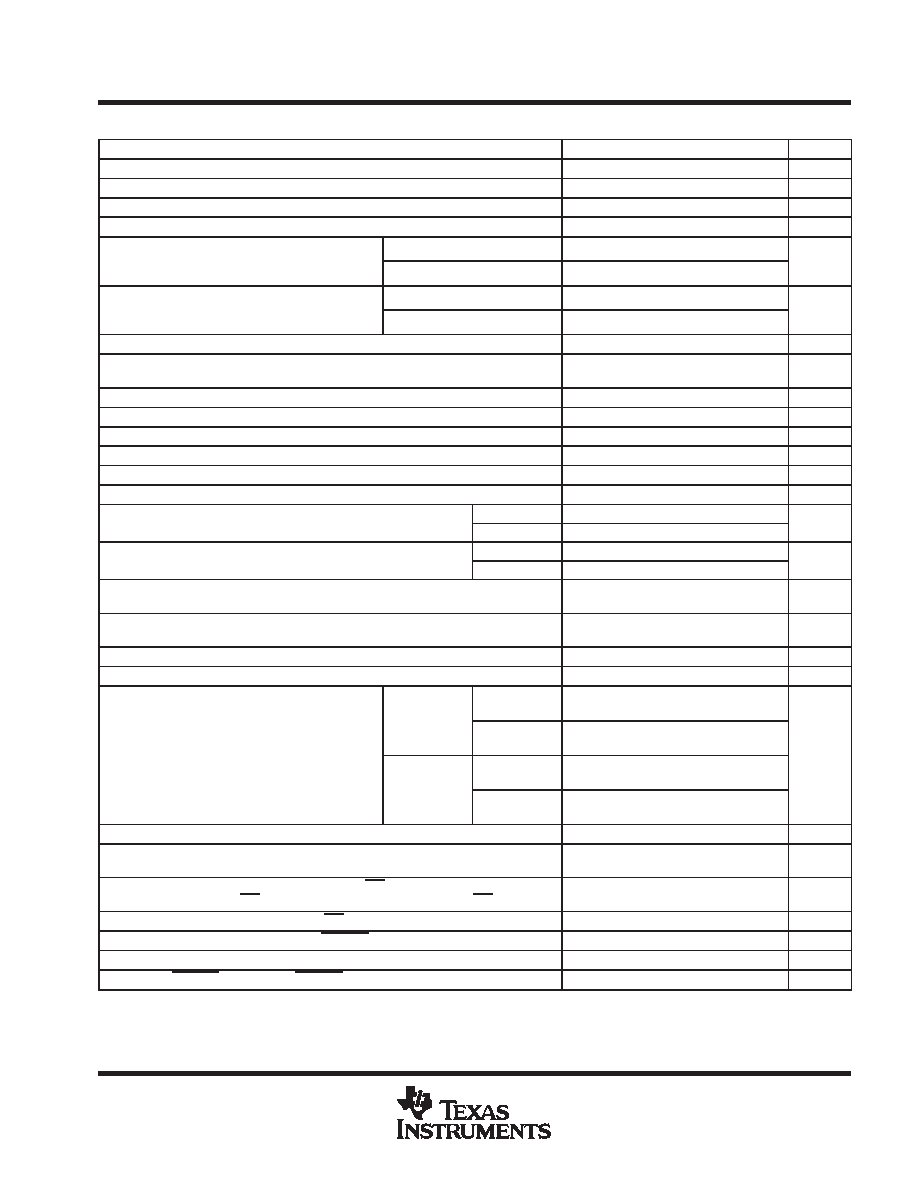

recommended operating conditions

MIN

NOM

MAX

UNIT

Supply voltage, VCC

3

3.3

5.5

V

Analog input voltage (see Note 3)

0

VCC

V

High level control input voltage, VIH

2.1

V

Low-level control input voltage, VIL

0.6

V

Setup time, tsu(CS-SCLK) CS falling edge before

SCLK rising edge (FS=1) or before SCLK falling

VCC = 4.5 V, SCLK = 20 MHz

20

ns

su(CS-SCLK)

SCLK rising edge (FS=1) or before SCLK falling

edge (when FS is active)

VCC = 3 V, SCLK = 20 MHz

30

ns

Hold time, CS rising edge after SCLK rising edge

(FS=1) or after SCLK falling edge (when FS is

VCC = 4.5 V

10

ns

(FS=1) or after SCLK falling edge (when FS is

active), th(SCLK-CS)

VCC = 3 V

15

ns

Delay time, delay from CS falling edge to FS rising edge, td(CSL-FSH)

0.5

SCLKs

Delay time, delay time from 16th SCLK falling edge to CS rising edge (FS is active),

td(SCLK16L-CSH)

0.5

SCLKs

Setup time, FS rising edge before SCLK falling edge, tsu(FSH-SCLKL)

20

ns

Hold time, FS hold high after SCLK falling edge, th(FSH-SCLKL)

30

37

ns

Pulse width, CS high time, twH(CS)

100

ns

Pulse width, FS high time, twH(FS)

0.75

1

SCLKs

SCLK cycle time, VCC = 3 V to 3.6V, tc(SCLK)

67

10000

ns

SCLK cycle time, VCC = 4.5 V to 5.5V, tc(SCLK)

50

10000

ns

Pulse width, SCLK low time, twL(SCLK)

VCC = 4.5 V

22

ns

Pulse width, SCLK low time, twL(SCLK)

VCC = 3 V

27

ns

Pulse width, SCLK high time, twH(SCLK)

VCC = 4.5 V

22

ns

Pulse width, SCLK high time, twH(SCLK)

VCC = 3 V

27

ns

Setup time, SDI valid before falling edge of SCLK (FS is active) or the rising edge of

SCLK (FS=1), tsu(DI-SCLK)

25

ns

Hold time, SDI hold valid after falling edge of SCLK (FS is active) or the rising edge

of SCLK (FS=1), th(DI-SCLK)

5

ns

Delay time, delay from CS falling edge to SDO valid, td(CSL-DOV)

25

ns

Delay time, delay from FS falling edge to SDO valid, td(FSL-DOV)

25

ns

VCC = 5.5 V

SDO = 0 pF

0.5 SCLK

+ 5

Delay time, delay from SCLK falling edge (FS is

active) or SCLK rising edge (FS=1) to SDO valid,

VCC = 5.5 V

SDO = 60 pF

0.5 SCLK

+ 24

ns

active) or SCLK rising edge (FS=1) to SDO valid,

td(SCLK-DOV)

VCC = 3.3 V

SDO = 0 pF

0.5 SCLK

+ 12

ns

VCC = 3.3 V

SDO = 60 pF

0.5 SCLK

+ 33

Delay time, delay from CS rising edge to SDO 3-state, td(CSH-DOZ)

80

ns

Delay time, delay from 17th SCLK rising edge (FS is active) or the 16th falling edge

(FS=1) to EOC falling edge, td(SCLK-EOCL)

45

ns

Delay time, delay from 16th SCLK falling edge to INT falling edge (FS =1) or from the

17th rising edge SCLK to INT falling edge (when FS active), td(SCLK-INT)

Min t(conv)

s

Delay time, delay from CS falling edge to INT rising edge, td(CSL-INTH)

50

ns

Delay time, delay from CS rising edge to CSTART falling edge, td(CSH-CSTARTL)

100

ns

Delay time, delay from CSTART rising edge to EOC falling edge, td(CSTARTH-EOCL)

50

ns

Pulse width, CSTART low time, twL(CSTART)

Min t(sample)

s

NOTE 3: When binary output format is used, analog input voltages greater than that applied to REFP convert as all ones (111111111111), while

input voltages less than that applied to REFM convert as all zeros (000000000000). The device is functional with reference down to

1 V. (VREFP VREFM 1); however, the electrical specifications are no longer applicable.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV2548MPWREP | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2553IDWG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2553IPWR | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2553IDWRG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2553IPWRG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV2548MFKB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLV2548MPWREP | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC EP 2B 200 KSPS ADC Ser. Out RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548QDW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12 Bit 200 kSPS Lo Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548QDWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Auto Cat 12B 200 kSPS ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548QDWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12 Bit 200 kSPS Lo Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。