- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV320AIC10CGQER (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PBGA80 PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC10CGQER |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| 封裝: | MICRO, PLASTIC, BGA-80 |

| 文件頁數(shù): | 8/57頁 |

| 文件大小: | 454K |

| 代理商: | TLV320AIC10CGQER |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

2–2

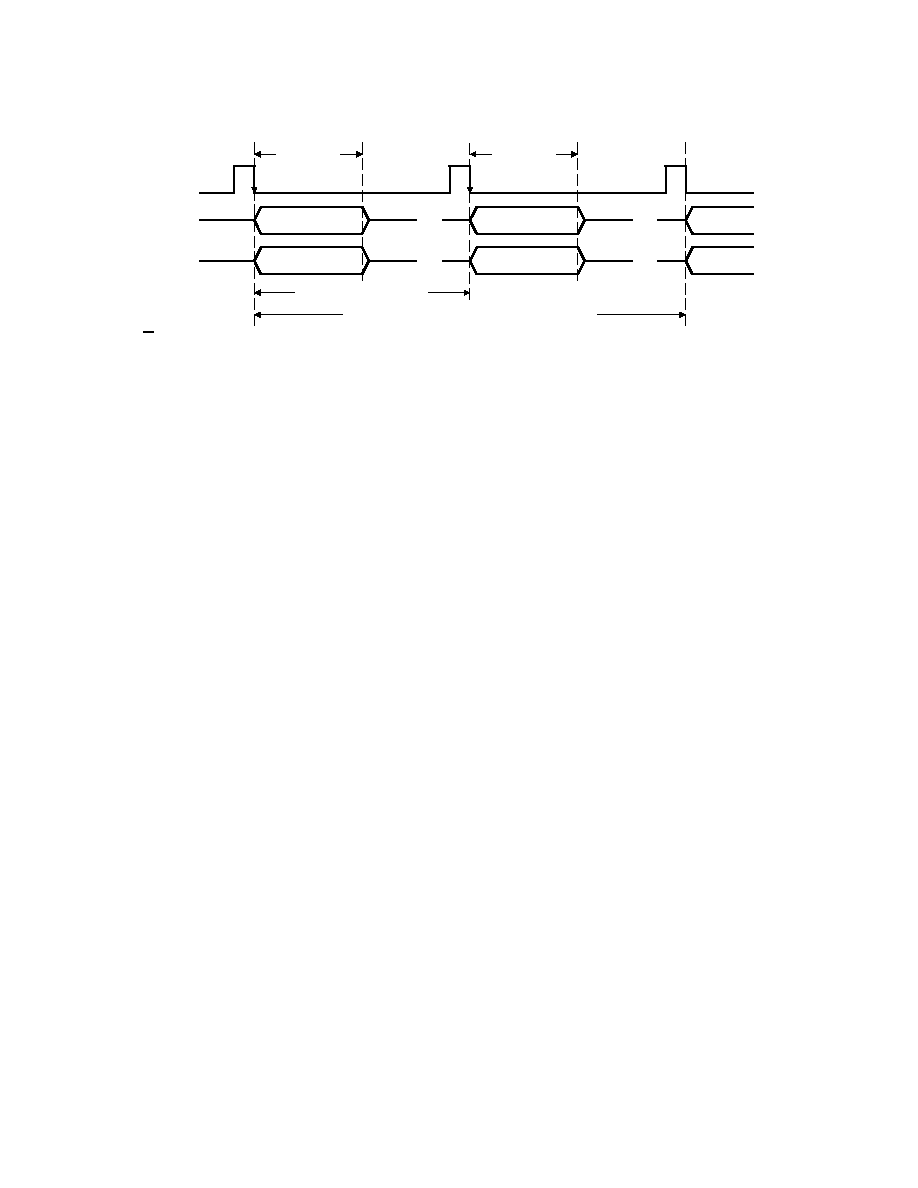

FS

DOUT

(16-bit)

DOUT

(15+1-bit)

Primary

Secondary

16 SCLKs

# SCLKs Per Sampling Period (See Note C)

16–bit ADC Data

15–bit ADC Data + M/S

M/S+ Register Data/

M/S+ All 0 (See Note A)

# SCLKs (See Note B)

M/S+ Register Data/

M/S+ All 0 (See Note A)

Primary

16 SCLKs

NOTES: A. M/S bit (D15) in the secondary communication is used to indicate whether the register data (address and content) come from a

master device or a slave device if read bit is set. Otherwise, it is all 0s except M/S bit (master: M/S=1, slave: M/S=0).

B. The number of SCLKs between FS (primary) and FS (secondary) is 128 if cascading devices are less than 5, or 256 if cascading

devices are greater than 4.

C. The number of SCLKs per data sampling period is 256 if cascading devices are less than 5, or 512 if cascading devices are greater

than 4.

Figure 2–2. Timing Sequence of ADC Channel (Primary and Secondary Communication)

2.1.3

DAC Signal Channel

DIN received the 16-bit serial data word (2s complement) from the host during the primary communication interval.

These 16-bit digital words, representing analog output signal before PGA, are clocked into the serial port (DIN) at

the falling edge of SCLK during the frame-sync interval, one bit for each SCLK and one word for each primary

communication interval. The data are converted to a pulse train by the sigma-delta DAC comprised of a

digital-interpolation filter and a digital 1-bit modulator. The output of the modulator is then passed to an internal

low-pass filter to complete the signal reconstruction. Finally, the resulting analog signal applied to the input of a

programmable-gain amplifier is capable of differentially driving a 600-ohm load at OUTP and OUTM. The timing

sequence is shown in Figure 2–3.

During secondary communication, the digital control and configuration data, together with the register address, are

clocked in through DIN (see Appendix A for register map). These 16-bit data are used either to initialize the register

or read out register content through DOUT. If a register initialization is not required, a no-operation word (D15-D9 are

all set to 0) can be used. If D12 is set to 1, the content of the control register, specified by D7-D0, are sent out through

DOUT during the same secondary communication (see Section 2.1.5). The timing sequence is shown in Figure 2–4.

The interpolation FIR filter can be bypassed by writing a 1 to bit D2 of control register 1. The whole DAC channel can

be turned off for power savings by writing 10 to bits D2 and D1 of control register 3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC10IGQER | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC11C | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC11I | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC11CPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC11IPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC10CPFB | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC10CPFBG4 | 功能描述:接口—CODEC 16-Bit Reg Trnscvr With 3-State Outputs RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC10EVM | 功能描述:音頻 IC 開發(fā)工具 TLV320AIC10 Eval Mod RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TLV320AIC10I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:General-Purpose 3V to 5.5V 16-bit 22-KSPS DSP CODEC |

| TLV320AIC10IGQER | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。