- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382647 > TMPP320C6202BGLW167 (Texas Instruments, Inc.) FIXED-POINT DIGITAL SIGNAL PROCESSORS PDF資料下載

參數(shù)資料

| 型號(hào): | TMPP320C6202BGLW167 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 52/83頁(yè) |

| 文件大小: | 1176K |

| 代理商: | TMPP320C6202BGLW167 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

TMS320C6211, TMS320C6211B

FIXED-POINT DIGITAL SIGNAL PROCESSORS

SPRS073K

AUGUST 1998

REVISED MARCH 2004

52

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

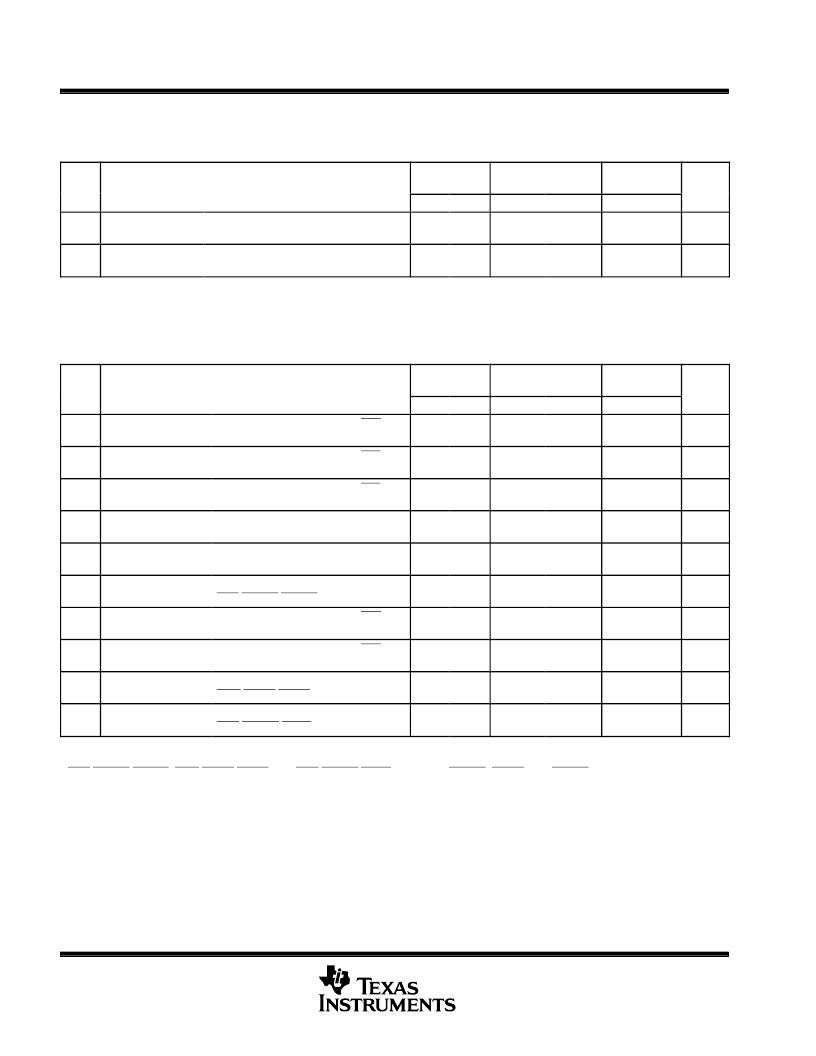

SYNCHRONOUS DRAM TIMING

timing requirements for synchronous DRAM cycles

(see Figure 22)

NO.

C6211

150

C6211

167

C6211BGFNA

150

C6211B

150

C6211B

167

UNIT

MIN

MAX

MIN

MAX

MIN

MAX

6

t

su(EDV-EKOH)

Setup time, read EDx valid before

ECLKOUT high

2.5

2.5

2.5

ns

7

t

h(EKOH-EDV)

Hold time, read EDx valid after

ECLKOUT high

1

2.5

2

ns

The C6211/C6211B SDRAM interface takes advantage of the internal burst counter in the SDRAM. Accesses default to incrementing 4-word

bursts, but random bursts and decrementing bursts are done by interrupting bursts in progress. All burst types can sustain continuous data flow.

switching characteristics over recommended operating conditions for synchronous DRAM

cycles

(see Figure 22

Figure 28)

NO.

PARAMETER

C6211

150

C6211

167

C6211BGFNA

150

C6211B

150

C6211B

167

UNIT

MIN

MAX

MIN

MAX

MIN

MAX

1

t

d(EKOH-CEV)

Delay time, ECLKOUT high to CEx

valid

1.5

6.5

1

6.5

1.2

6.5

ns

2

t

d(EKOH-BEV)

Delay time, ECLKOUT high to BEx

valid

6.5

6.5

6.5

ns

3

t

d(EKOH-BEIV)

Delay time, ECLKOUT high to BEx

invalid

1.5

1

1.2

ns

4

t

d(EKOH-EAV)

Delay time, ECLKOUT high to EAx

valid

6.5

6.5

6.5

ns

5

t

d(EKOH-EAIV)

Delay time, ECLKOUT high to EAx

invalid

1.5

1

1.2

ns

8

t

d(EKOH-CASV)

Delay time, ECLKOUT high to

ARE/SDCAS/SSADS valid

1.5

6.5

1

6.5

1.2

6.5

ns

9

t

d(EKOH-EDV)

Delay time, ECLKOUT high to EDx

valid

7

7

7

ns

10

t

d(EKOH-EDIV)

Delay time, ECLKOUT high to EDx

invalid

1.5

1

1.2

ns

11

t

d(EKOH-WEV)

Delay time, ECLKOUT high to

AWE/SDWE/SSWE valid

1.5

6.5

1

6.5

1.2

6.5

ns

12

t

d(EKOH-RAS)

Delay time, ECLKOUT high to

AOE/SDRAS/SSOE valid

1.5

6.5

1

6.5

1.2

6.5

ns

The C6211/C6211B SDRAM interface takes advantage of the internal burst counter in the SDRAM. Accesses default to incrementing 4-word

bursts, but random bursts and decrementing bursts are done by interrupting bursts in progress. All burst types can sustain continuous data flow.

ARE/SDCAS/SSADS, AWE/SDWE/SSWE, and AOE/SDRAS/SSOE operate as SDCAS, SDWE, and SDRAS, respectively, during SDRAM

accesses.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320C6202BGLZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6203BGLZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6211BGLZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6202BGLZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6203BGNZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMPR28051 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| TMPR28051-3-SL5 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| TMPR28051-SL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET MAPPER|QFP|208PIN|PLASTIC |

| TMPR3904F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

| TMPR3907F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。