- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320AV110 (Texas Instruments, Inc.) MPEG Audio Decoder(MPEG音頻譯碼器) PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320AV110 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | MPEG Audio Decoder(MPEG音頻譯碼器) |

| 中文描述: | MPEG音頻解碼器(的MPEG音頻譯碼器) |

| 文件頁(yè)數(shù): | 3/38頁(yè) |

| 文件大小: | 796K |

| 代理商: | TMS320AV110 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

TMS320AV110

MPEG AUDIO DECODER

SCSS013C – MAY 1993 – REVISED AUGUST 1995

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

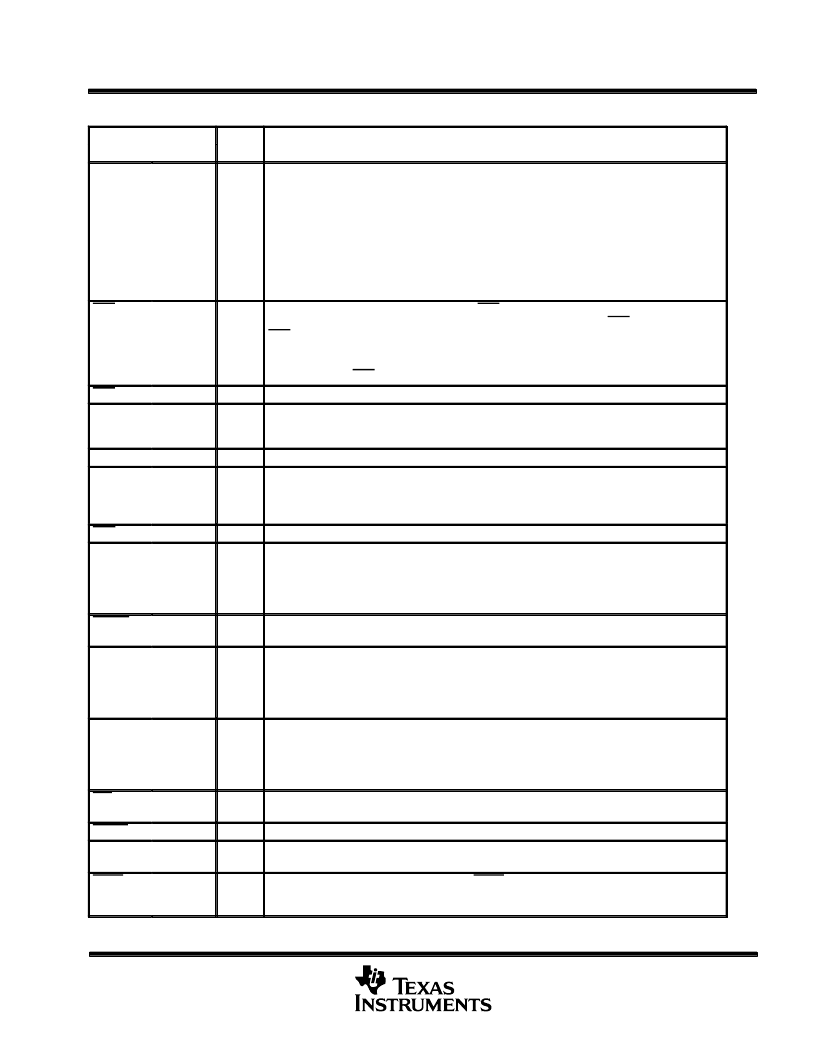

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

NO.

58

63

64

65

66

68

69

71

72

74

O

DRAM address bus output

BOF

27

O

Beginning of frame signal. The falling edge of BOF signals the beginning of a new audio frame. The

first bit of the new frame is on the PCMDATA output at the falling edge of BOF. The falling edge of

BOF will occur synchronous to the OSCIN clock and will occur from one to two OSCIN clocks prior

to the first rising edge of SCLK after a rising LRCLK edge. It varies from one to two clocks because

OSCIN may be asynchronous to SCLK. The low pulse width is four periods of the OSCIN clock, and

the rising edge of BOF is also synchronous to OSCIN.

CAS

48

O

DRAM column address strobe

CLK90

28

I

90-kHz reference clock input. Optionally used for audio/video synchronization. Provides the clock

for the internal reference counter. CLK90 should be tied to GND if the ’AV110 is not used for

synchronization.

CLKOUT

8

O

Buffered system clock (OSCIN) output

D3

D2

D1

D0

51

52

56

57

I/O

DRAM data bus

DCS

94

I

Register access chip select

DMPH1

DMPH0

26

25

O

Decoded deemphasis select output. The audio deemphasis information is decoded from the header

and is output on DMPH0 and DMPH1. The information is also available in the DMPH register, and

an interrupt is generated on a change in the DMPH value. The interrupt and DMPH0 and DMPH1

change state when the corresponding frame is at the PCM output stage. (DMPH1, DMPH0) 00 =

none, 01 = 50/15 microseconds, 10 = reserved, 11 = CCITT J.17.

DSTRB

93

I

Data strobe. DSTRB is used to load compressed audio data into the ’AV110 in both bit-serial and

byte-parallel modes.

FS1

FS0

23

22

O

Decoded sampling frequency output. The ’AV110 decodes the sampling frequency from the MPEG

header. This data is also available in the PCM_FS register. The FS0 and FS1 terminals reflect the

current sampling frequency when the first data point of the frame is at the PCM output stage. If

enabled and the FS value has changed, an interrupt is generated. (FS1, FS0): 00 = 44.1 kHz,

01 = 48 kHz, 10 = 32 kHz, 11 = reserved.

GND

2, 5, 15,

21, 30, 38,

47, 54, 62,

75, 90, 98,

105

Ground

IRQ

101

O

Interrupt request output. This is an active-low pulse that is triggered by one of the bits being set in

the INTR register, unless the corresponding bit is masked in the INTR_EN register.

IRQOD

102

O

Interrupt request, open-drain output

LRCLK

17

O

Left/right channel PCM-data-sampling clock. A high logic level selects left PCM data, and a low logic

level selects right PCM data.

MUTE

117

I

Forces the output of muted PCM data when MUTE is low. PCM muting is in effect if either this line

or the MUTE register is asserted. Muting does not affect the actual audio decoding process (see

Table 1).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320AV120 | MPEG Audio Decoder(MPEG音頻譯碼器) |

| TMS320AV220 | Video CD MPEG Decoder(視頻CD MPEG編碼器) |

| TMS320AV410 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV411 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV420 | Digital NTSC Encoder(數(shù)字NTSC編碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320AV120 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Decoder & Support |

| TMS320AV120FN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Decoder & Support |

| TMS320AV220PCM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Audio/Video Decoder for MPEG |

| TMS320AV410 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV410PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。