- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368677 > TMS370C777AYYZ Microcontroller PDF資料下載

參數(shù)資料

| 型號: | TMS370C777AYYZ |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 7/48頁 |

| 文件大?。?/td> | 711K |

| 代理商: | TMS370C777AYYZ |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

TMS370Cx36

8-BIT MICROCONTROLLER

SPNS039B – JANUARY 1996 – REVISED FEBRUARY 1997

7

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

central processing unit (CPU) (continued)

The ST, status-bit notation, and status-bit definitions are shown in Table 3.

Table 3. Status Registers

ááááááááááááááááááááááááááááá

ááááááááááááááááááááááááááááá

ááááááááááááááááááááááááááááá

ááááááááááááááááááááááááááááá

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

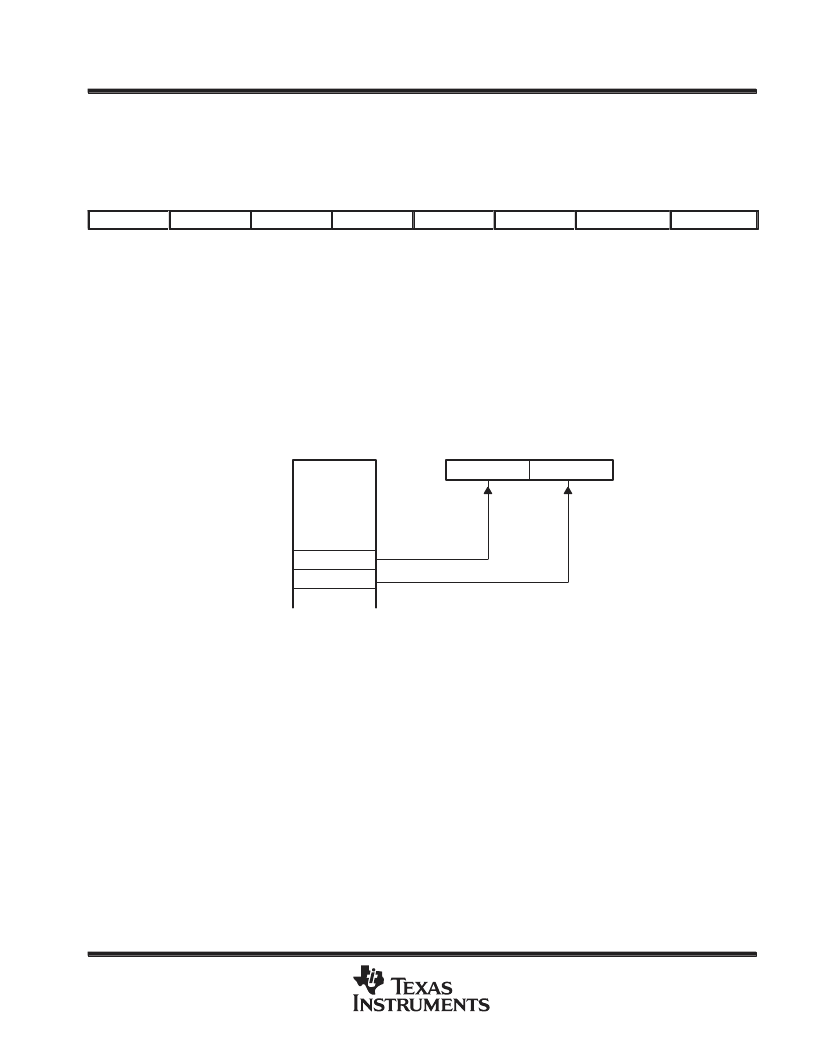

program counter (PC)

The contents of the PC point to the memory location of the next instruction to be executed. The PC consists

of two 8-bit registers in the CPU: the program counter high (PCH) and program counter low (PCL). These

registers contain the most significant byte (MSbyte) and least significant byte (LSbyte) of a 16-bit address.

During reset, the contents of the reset vector (7FFEh, 7FFFh) are loaded into the PC. The PCH (MSbyte of the

PC) is loaded with the contents of memory location 7FFEh, and the PCL (LSbyte of the PC) is loaded with the

contents of memory location 7FFFh. Figure 2 shows this operation using an example value of 4000h as the

contents of the reset vector.

Memory

Program Counter (PC)

40

00

PCH

PCL

40

00

0000h

7FFEh

7FFFh

Figure 2. Program Counter After Reset

memory map

The TMS370Cx36 architecture is based on the Von Neuman architecture, where the program memory and data

memory share a common address space. All peripheral input/output is memory mapped in this same common

address space. As shown in Figure 3, the TMS370Cx36 provides memory-mapped RAM, ROM, EPROM, data

EEPROM, I/O pins, peripheral functions, and system-interrupt vectors.

The peripheral file contains all I/O port control, peripheral status and control, EEPROM, EPROM, and

system-wide control functions. The peripheral file is located between 1000h to 107Fh and is divided logically

into eight peripheral file frames of 16 bytes each. The eight PF frames consist of five control frames and three

reserved frames.Each on-chip peripheral is assigned to a separate frame through which peripheral control and

data information are passed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS370C792FNT | 8-BIT MICROCONTROLLER |

| TMS370C792NJT | 8-BIT MICROCONTROLLER |

| TMS370C020AFNL | 8-BIT MICROCONTROLLER |

| TMS370C020AFNT | 8-BIT MICROCONTROLLER |

| TMS370C020AN2A | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS370C792FNT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| TMS370C792N2T | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMS370P16A27FNQ | 制造商:Texas Instruments 功能描述: |

| TMS37112B3 WAF | 制造商:Texas Instruments 功能描述: |

| TMS37122DPWRG4 | 制造商:Texas Instruments 功能描述:3D Analog Front-end, TITL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。