- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383961 > TMX320DM647ZUT720 (Texas Instruments, Inc.) Digital Media Processor PDF資料下載

參數(shù)資料

| 型號: | TMX320DM647ZUT720 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media Processor |

| 中文描述: | 數(shù)字媒體處理器 |

| 文件頁數(shù): | 147/166頁 |

| 文件大小: | 1341K |

| 代理商: | TMX320DM647ZUT720 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁當(dāng)前第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

www.ti.com

P

6.18.3 Peripheral Register Description(s)

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372–MAY 2007

terminals (SGMII0RXN: SGMII0RXP, SGMII1RXN: SGMII1RXP) into the required GMAC GMII signals.

The SGMII transmit interface converts the GMAC GMII data into the required encoded differential transmit

output terminals (SGMII0TXN: SGMII0TXP, SGMII1TXN: SGMII1TXP). The GMAC does not source the

transmit error signal. Any transmit frame from the GMAC with an error (ie., underrun) will be indicated as

an error by an error CRC.

NOTE

SGMII1 is pinned out only in the DM648 device. DM647 device has only one SGMII port

(SGMII0).

Table 6-64

through

Table 6-67

list the registers.

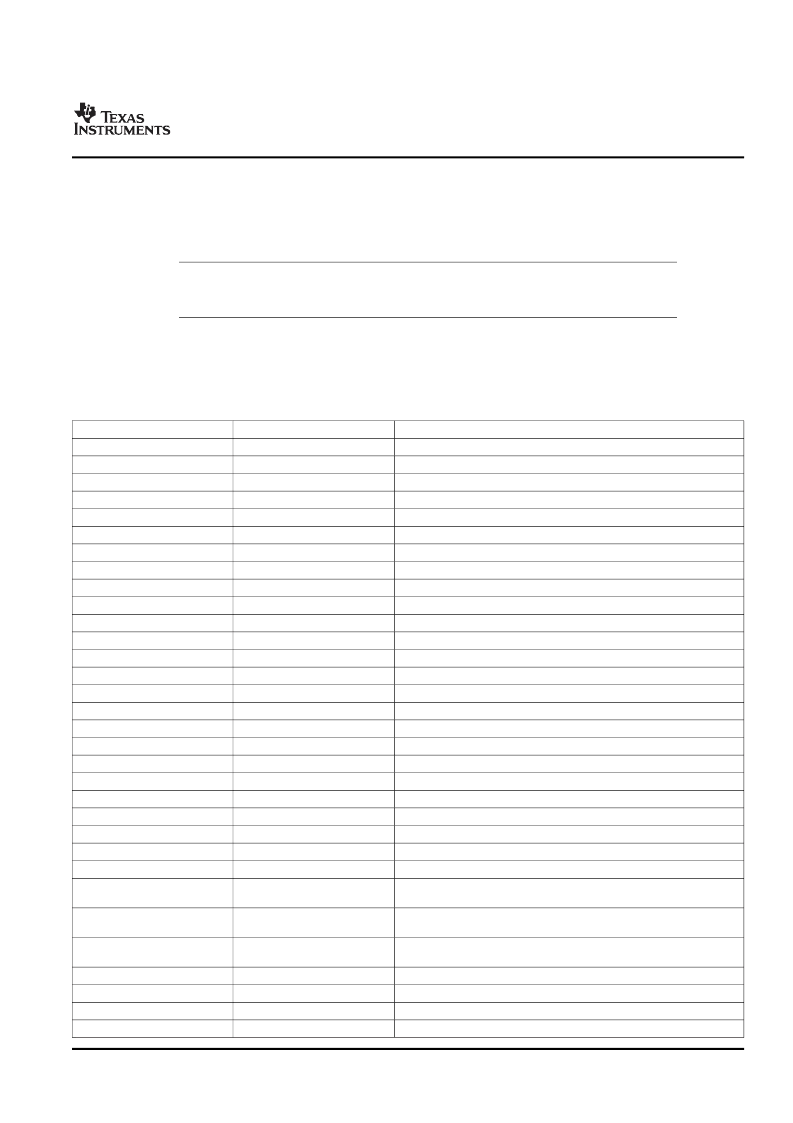

Table 6-64. 3-port Gigabit Switch Registers

HEX ADDRESS RANGE

0x02D0 3000

0x02D0 3004

0x02D0 3008

0x02D0 300C

0x02D0 3010

0x02D0 3014

0x02D0 3018

0x02D0 301C

0x02D0 3020

0x02D0 3024

0x02D0 3028

0x02D0 302C

0x02D0 3030

0x02D0 3034

0x02D0 3038

0x02D0 303C

0x02D0 3040

0x02D0 3044

0x02D0 3048

0x02D0 304C

0x02D0 3050

0x02D0 3054

0x02D0 3058

0x02D0 305C

0x02D0 3060

0x02D0 3064

REGISTER NAME

CPSW_Id_Ver

CPSW_Control

CPSW_Soft_Reset

CPSW_Stat_Port_En

CPSW_PTYPE

P0_Max_Blks

P0_BLK_CNT

P0_Flow_Thresh

P0_Port_VLAN

P0_Tx_Pri_Map

GMAC0_Gap_Thresh

GMAC0_SA_LO

GMAC0_SA_HI

P1_Max_Blks

P1_BLK_CNT

P1_Flow_Thresh

P1_Port_VLAN

P1_Tx_Pri_Map

GMAC1_Gap_Thresh

GMAC1_SA_LO

GMAC1_SA_HI

P2_Max_Blks

P2_BLK_CNT

P2_Flow_Thresh

P2_Port_VLAN

P2_Tx_Pri_Map

DESCRIPTION

3pGSw ID Version Register

3pGSw Switch Control Register

3pGSw Soft Reset Register

3pGSw Statistics Port Enable Register

3pGSw Transmit Priority Type Register

3pGSw Port 0 Maximum FIFO blocks Register

3pGSw Port 0 FIFO Block Usage Count (read only)

3pGSw Port 0 Flow Control Threshold Register

3pGSw Port 0 VLAN Register

3pGSw Port 0 Tx Header Pri to Switch Pri Mapping Register

3pGSw GMAC0 Short Gap Threshold Register

3pGSw GMAC0 Source Address Low Register

3pGSw GMAC0 Source Address High Register

3pGSw Port 1 Maximum FIFO blocks Register

3pGSw Port 1 FIFO Block Usage Count (read only)

3pGSw Port 1 Flow Control Threshold Register

3pGSw Port 1 VLAN Register

3pGSw Port 1 Tx Header Priority to Switch Pri Mapping Register

3pGSw GMAC1 Short Gap Threshold Register

3pGSw GMAC1 Source Address Low Register

3pGSw GMAC1 Source Address High Register

3pGSw Port 2 Maximum FIFO blocks Register

3pGSw Port 2 FIFO Block Usage Count (read only)

3pGSw Port 2 Flow Control Threshold Register

3pGSw Port 2 VLAN Register

3pGSw Port 2 Tx (CPDMA RX) Header Priority to Switch Pri Mapping

Register

3pGSw CPDMA TX (Port 2 Rx) Pkt Priority to Header Priority Mapping

Register

3pGSw CPDMA RX (Port 2 Tx) Switch Priority to DMA channel

Mapping Register

Reserved

GMAC0 ID/Version Register

GMAC0 Mac Control Register

GMAC0 Mac Status Register

0x02D0 3068

CPDMA_Tx_Pri_Map

0x02D0 306C

CPDMA_Rx_Ch_Map

0x02D0 3070 - 0x02D0 307C

0x02D0 3080

0x02D0 3084

0x02D0 3088

Reserved

GMAC0_IDVER

GMAC0_MacControl

GMAC0_MacStatus

Submit Documentation Feedback

Peripheral Information and Electrical Specifications

147

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320DM647ZUT900 | Digital Media Processor |

| TMX320DM648ZUT720 | Digital Media Processor |

| TMX320DM648ZUT900 | Digital Media Processor |

| TMS320LC31PQL | DIGITAL SIGNAL PROCESSORS |

| TMX320C6414TGLZ | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM647ZUT900 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM648ACUT7 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648ACUT9 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648AZUT7 | 制造商:Texas Instruments 功能描述: |

| TMX320DM648CUT7 | 制造商:Texas Instruments 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。