- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385942 > TNETA1630 (Texas Instruments, Inc.) 622.08-MHz Clock-Recovery Device(622.08-MHz時(shí)鐘發(fā)生裝置) PDF資料下載

參數(shù)資料

| 型號(hào): | TNETA1630 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 622.08-MHz Clock-Recovery Device(622.08-MHz時(shí)鐘發(fā)生裝置) |

| 中文描述: | 622.08 MHz的時(shí)鐘恢復(fù)裝置(622.08 MHz的時(shí)鐘發(fā)生裝置) |

| 文件頁(yè)數(shù): | 1/4頁(yè) |

| 文件大小: | 70K |

| 代理商: | TNETA1630 |

TNETA1630

622.08-MHz CLOCK-GENERATION DEVICE

SDNS029C – OCTOBER 1994 – REVISED DECEMBER 1995

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Generates a 622.08-MHz Clock From a

19.44-MHz TTL Clock

Provides Differential Pseudo-ECL (PECL)

Outputs

Operates From a SIngle 5-V Power Supply

Packaged in 20-Pin Plastic Small-Outline

(DW) Package

description

The TNETA1630 is a 622.08-MHz clock-

generation device that utilizes a TTL-clock input at

19.44 MHz. The 622.08-MHz clock is provided on

differential pseudo-ECL (PECL) outputs. The

device operates from a single 5-V power supply.

An internal second-order low-pass filter is used to

reduce jitter.

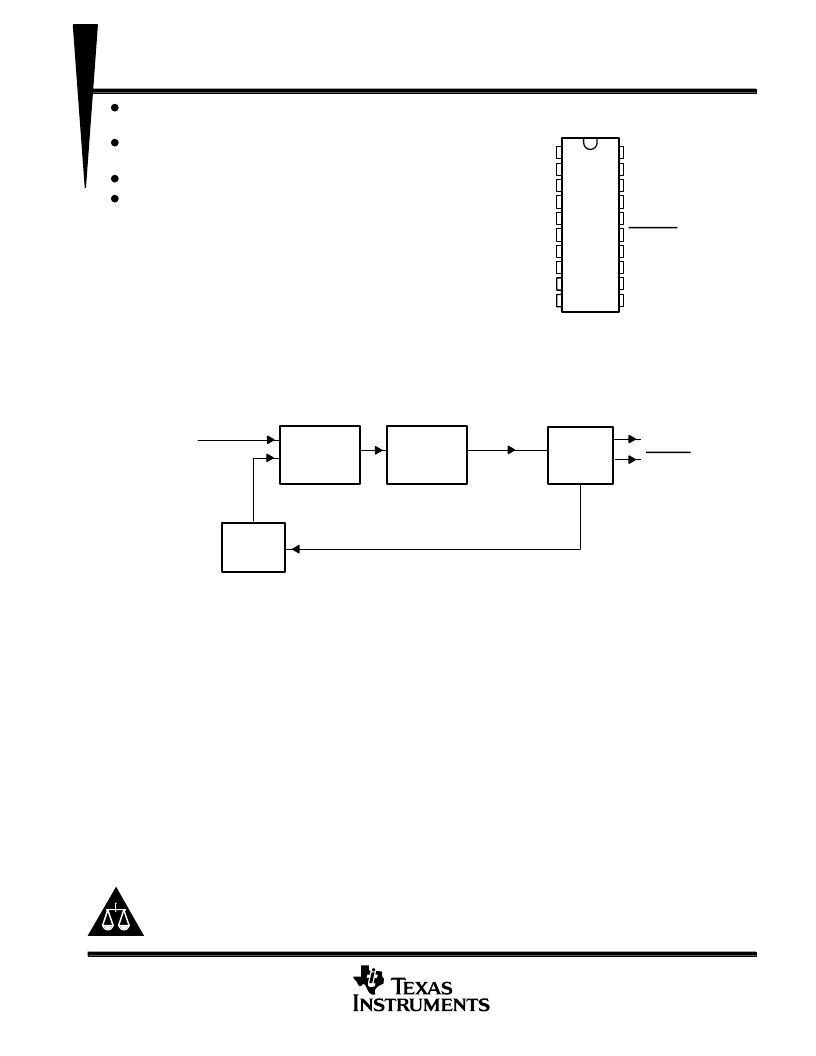

functional block diagram

Frequency-

and-

Phase

Detector

Charge

Pump/Loop

Filter

Voltage-

Controlled

Oscillator

Divide by

32

CLKOUT

CLKOUT

CLKIN

Copyright

1995, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

V

CC

V

CC

NC

V

CC

CLKIN

GND

GND

GND

V

CC

GND

GND

GND

GND

V

CC

CLKOUT

CLKOUT

V

CC

NC

V

CC

V

CC

DW PACKAGE

(TOP VIEW)

NC – No internal connection

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TO-252 | TO-252 (MP-3Z) |

| TODX2402 | FIBER OPTIC TRANSCEIVING MODULE |

| TOLD9321 | VLD Telchnical Data |

| TOLD9321F | VLD Telchnical Data |

| TORX178S | FIBER OPTIC RECEIVING MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1630DW | 制造商:Texas Instruments 功能描述: |

| TNETC400E-CM | 制造商:Texas Instruments 功能描述: |

| TNETC400EE-CM | 制造商:Texas Instruments 功能描述: |

| TNETC4030BPCE | 制造商:Texas Instruments 功能描述: |

| TNETC4040CPPM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。