- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98281 > TPS40197RGYR (TEXAS INSTRUMENTS INC) SWITCHING CONTROLLER, 520 kHz SWITCHING FREQ-MAX, PQCC16 PDF資料下載

參數(shù)資料

| 型號(hào): | TPS40197RGYR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | SWITCHING CONTROLLER, 520 kHz SWITCHING FREQ-MAX, PQCC16 |

| 封裝: | PLASTIC, MO-241BB, VQFN-16 |

| 文件頁(yè)數(shù): | 5/30頁(yè) |

| 文件大小: | 931K |

| 代理商: | TPS40197RGYR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

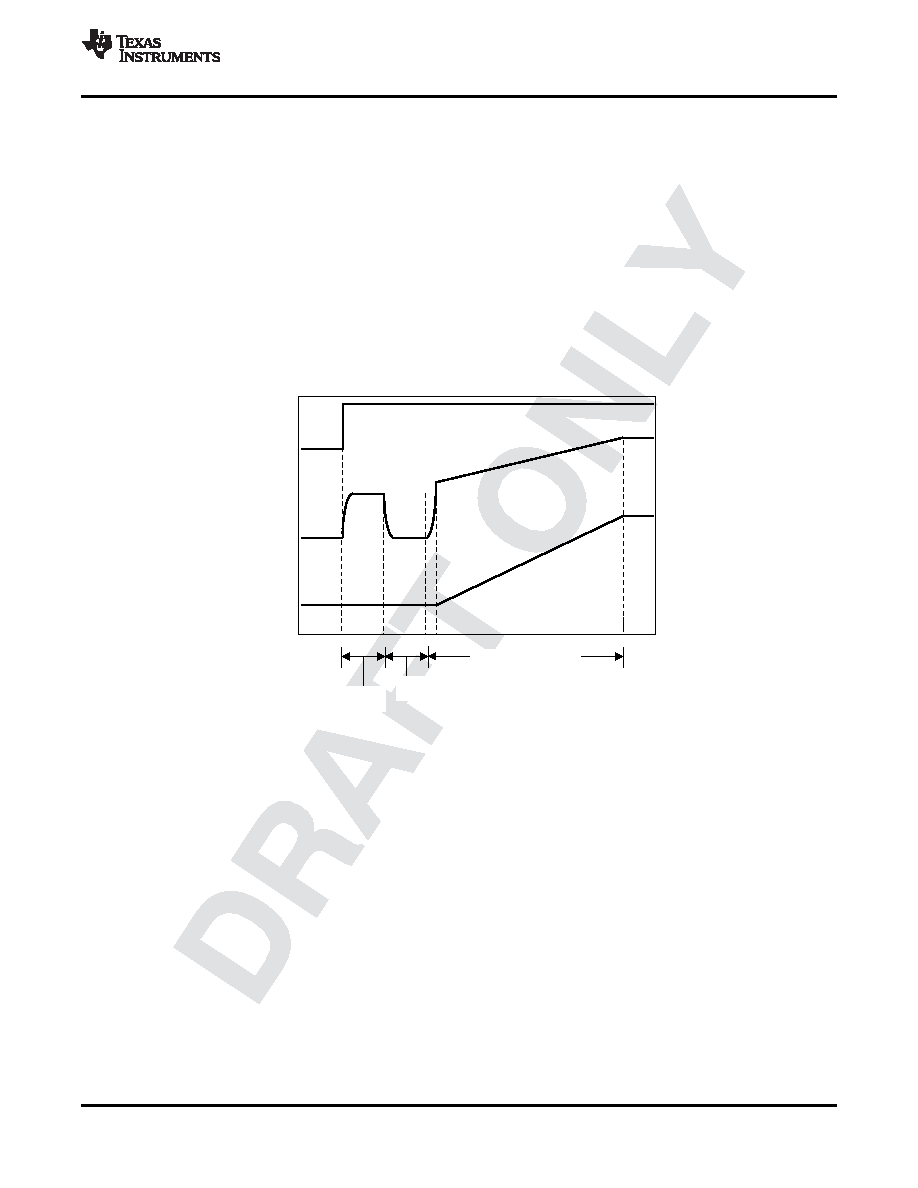

EN

COMP

VOUT

SC Threshold Configured

(1.15 ms)

Compensation Network Zeroed

(1.15 ms)

Soft-Start Time (5.5 ms)

UDG-08099

TI Information — Selective Disclosure

www.ti.com

SLUS886 – NOVEMBER 2008

UVLO

When the input voltage is below the UVLO threshold, the device holds all gate drive outputs in the low (OFF)

state. When the input rises above the UVLO threshold, and the EN pin is above the turn ON threshold, the

oscillator begins to operate and the start-up sequence is allowed to begin. The UVLO level is internally fixed at

4.2 V.

Startup Sequence and Timing

The TPS40197 startup sequence is as follows. After input power is applied, the 5-V onboard regulator initiates.

Once this regulator comes up, the device goes through a period where it samples the impedance at the COMP

pin and determines the short-circuit protection threshold voltage, by placing 400 mV on the COMP pin for

approximately 1.15 ms. During this time, the current is measured and compared against internal thresholds to

select the short circuit protection threshold. After this, the COMP pin is brought low for 1.15 ms. This ensures

that the feedback loop is preconditioned at startup and no sudden output rise occurs at the output of the

converter when the converter is allowed to start switching. After these initial 2.3 ms, the internal soft-start circuitry

is engaged and the converter is allowed to start as shown in Figure 15.

Figure 15. Startup Sequence

Selecting the Short Circuit Current

A short circuit in the TPS40197 is detected by sensing the voltage drop across the low-side FET when it is on,

and across the high-side FET when it is on. If the voltage drop across either FET exceeds the short-circuit

threshold in any given switching cycle, a counter increments one count. If the voltage across the high-side FET

was higher than the short circuit threshold, that FET is turned off early. If the voltage drop across either FET

does not exceed the short circuit threshold during a cycle, the counter is decremented for that cycle. If the

counter fills up (a count of 7) a fault condition is declared and the drivers turn off both MOSFETs. After a timeout

of approximately 50 ms, the controller attempts to restart. If a short circuit continues at the output, the current

quickly ramps up to the short-circuit threshold and another fault condition is declared and the process of waiting

for the 50 ms and attempting to restart repeats. The low-side threshold increases as the low-side on time

decreases due to blanking time and comparator response time. See Figure 13 for changes in the threshold as

the low-side FET conduction time decreases.

Copyright 2008, Texas Instruments Incorporated

13

Product Folder Link(s): TPS40197

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS40200MDREPG4 | SWITCHING CONTROLLER, 500 kHz SWITCHING FREQ-MAX, PDSO8 |

| TPS40211DRCTG4 | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PDSO10 |

| TPS40210DGQG4 | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PDSO10 |

| TPS40304ADRCT | SWITCHING CONTROLLER, PQCC10 |

| TPS40304ADRCR | SWITCHING CONTROLLER, PQCC10 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS40197RGYT | 功能描述:DC/DC 開(kāi)關(guān)控制器 4.5-14V Inp Synch Buck Cntrlr RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開(kāi)關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| TPS40-20 | 制造商:TOTAL-POWER 制造商全稱:TOTAL-POWER 功能描述:40 WATT OPEN - FRAME SWITCHING POWER SUPPLY |

| TPS40200 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:WIDE INPUT RANGE NON-SYNCHRONOUS VOLTAGE MODE CONTROLLER |

| TPS40200_08 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:WIDE INPUT RANGE NON-SYNCHRONOUS VOLTAGE MODE CONTROLLER |

| TPS40200_081 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:WIDE INPUT RANGE NON-SYNCHRONOUS VOLTAGE MODE CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。