- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373685 > TQ8103 (TriQuint Semiconductor,Inc.) 622 Mb/s Clock & Data Recovery PDF資料下載

參數(shù)資料

| 型號(hào): | TQ8103 |

| 廠商: | TriQuint Semiconductor,Inc. |

| 英文描述: | 622 Mb/s Clock & Data Recovery |

| 中文描述: | 622 Mb / s的時(shí)鐘 |

| 文件頁(yè)數(shù): | 1/9頁(yè) |

| 文件大小: | 194K |

| 代理商: | TQ8103 |

T

R

I Q

U

I

N

T

S E M I C O N D U C T O R , I N C .

T

P

1

For additional information and latest specifications, see our website:

www.triquint.com

The TQ8103 is a monolithic clock and data recovery (CDR) IC that receives

NRZ data, extracts the high-speed clock, and presents the separated data

and clock as its outputs. This device is designed specifically for SONET

OC-12 and SDH STM-4 applications at 622 Mb/s.

Its on-chip phase-locked loop (PLL) generates a stable 622.08 Mb/s

reference based upon an external 38.88 MHz TTL reference. The PLL is

based on a VCO constructed from integrated reactive components, which

form a low-jitter, high-Q differential tank circuit. Both frequency- and

phase-detect circuits reliably acquire and hold lock in worst-case SONET

jitter conditions and scrambling patterns. The lock-detect circuitry signals

when the CDR acquires frequency lock.

Typical SONET/SDH system applications for the TQ8103 include:

Transmission system transport cards

Switch and cross-connect line cards

ATM physical layer interfaces

Test equipment

Add/drop multiplexers

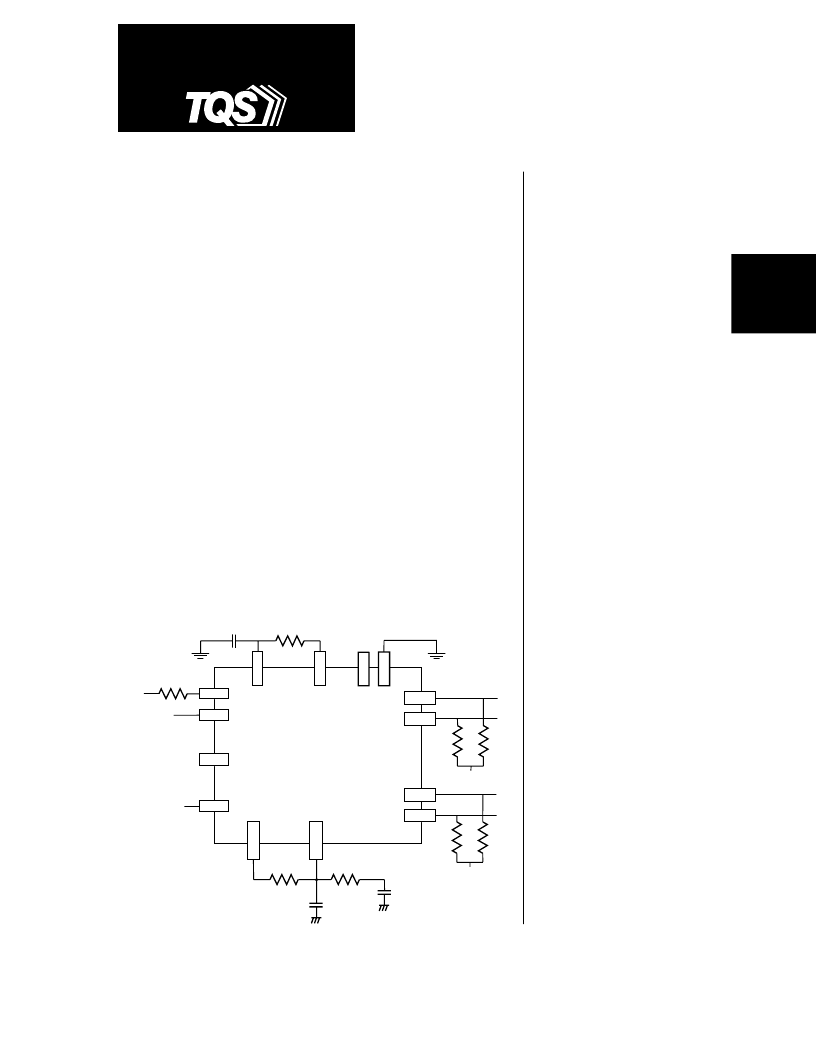

Figure 1. Typical Application

TQ8103

622 Mb/s Clock

& Data Recovery

Features

Single-chip CDR circuit for

622 Mb/s data

Exceeds Bellcore and ITU jitter

tolerance maps

Single-ended ECL input has loop-

through path for external 50 ohm

termination to minimize stubs

and reflections

Clock and data outputs are

differential ECL

Provides complete high-speed

OC-12/STM-4 solution when

used with TQ8101 or TQ8105

Mux/Demux/Framer/PLL

External loop filter requires

simple passive network

Maintains clock in absence of data

28-pin leaded chip carrier

Can be used with a high-speed

external clock

O

L

CKREF

V

C

D

OUTP

SINI

SINO

X

S

S

V

REF

CK

OUTP

CK

OUTN

V

TT

ECL data in

(single-ended)

38.88-MHz TTL

clock oscillator

20K

62

1 mF

50

V

TT

10K

1000 pF

V

TT

D

OUTN

50

50

1000 pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TQ8105 | SONET/SDH Transceivers |

| TQ8106 | SONET/SDH Transceivers |

| TQ8213 | Multiplexer |

| TQ9132B | 3V Cellular TDMA/AMPS Power Amplifier IC |

| TQ9147B | 2-Stage AMPS Power Amplifier IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TQ8103-Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Clock/Data Recovery |

| TQ8105 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:SONET/SDH Transceivers |

| TQ8106 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:SONET/SDH Transceivers |

| TQ8213 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:Multiplexer |

| TQ8214 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Industrial Control IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。