- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄272328 > TS(X)PC603EMGB/C2LN 32-BIT, 80 MHz, RISC PROCESSOR, CBGA255 PDF資料下載

參數(shù)資料

| 型號: | TS(X)PC603EMGB/C2LN |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 80 MHz, RISC PROCESSOR, CBGA255 |

| 封裝: | CERAMIC, BGA-255 |

| 文件頁數(shù): | 23/38頁 |

| 文件大小: | 632K |

| 代理商: | TS(X)PC603EMGB/C2LN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

TSPC603E

3/38

A. GENERAL DESCRIPTION

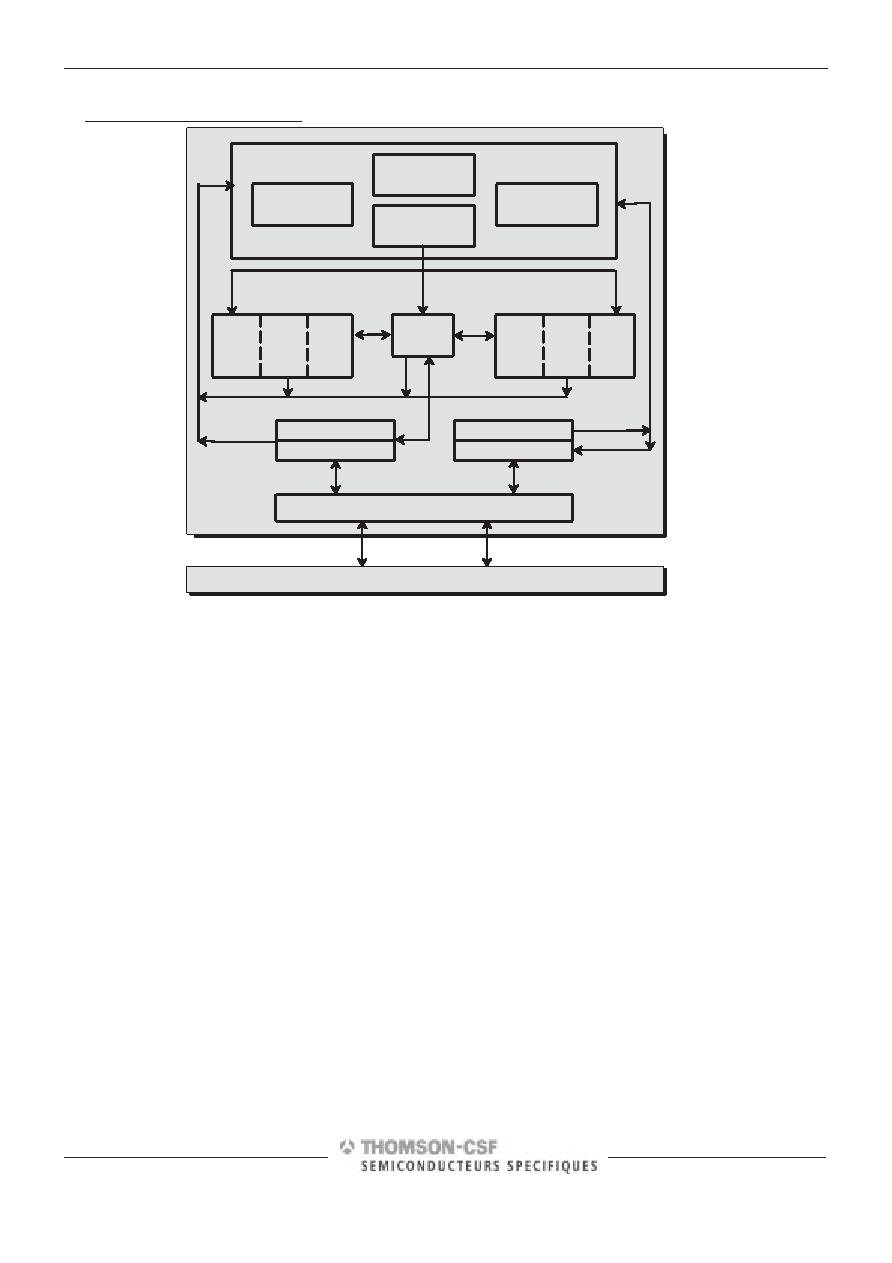

Completion

Unit

Fetch

Unit

Dispatch

Unit

Branch

Unit

Integer

Unit

Gen

Reg

Unit

Gen

Re-

name

Load/

Store

Unit

FP

Re-

name

FP

Reg

File

Float

Unit

D MMU

16K Data Cache

I MMU

16K Inst. Cache

Bus Interface Unit

System Bus

32b

address

64b

data

Figure 1 : Block diagram

1. INTRODUCTION

The 603e is a low-power implementation of the PowerPC microprocessor family of reduced instruction set commuter (RISC) micro-

processors. The 603e implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer

data types of 8, 16 and 32 bits, and floating-point data types of 32 and 64 bits. For 64-bit PowerPC microprocessors, the PowerPC

architecture provides 64-bit integer data types, 64-bit addressing, and other features required to complete the 64-bit architecture.

The 603e provides four software controllable power-saving modes. Three of the modes (the nap, doze, and sleep modes) are static in

nature, and progressively reduce the amount of power dissipated by the processor. The fourth is a dynamic power management

mode that causes the functional units in the 603e to automatically enter a low-power mode when the functional units are idle without

affecting operational performance, software execution, or any external hardware.

The 603e is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can execute

out of order for increased performance ; however, the 603e makes completion appear sequential.

The 603 e integrates five execution units - an integer unit (IU), a floating-point unit (FPU), a branch processing unit (BPU), a load/store

unit (LSU) and a system register unit (SRU). The ability to execute five instructions in parallel and the use of simple instructions with

rapid execution times yield high efficiency and throughput for 603e-based systems. Most integer instructions execute in one clock

cycle. The FPU is pipelined so a single-precision multiply-add instruction can be issued every clock cycle.

The 603e provides independent on-chip, 16 Kbyte, four-way set-associative, physically addressed caches for instructions and data

and on-chip instruction and data memory management units (MMUs). The MMUs contain 64-entry, two-way set-associative, data

and instruction translation lookaside buffers (DTLB and ITLB) that provide support for demand-paged virtual memory address

translation and variable-sized block translation. The TLBs and caches use a least recently used (LRU) replacement algorithm. The

603e also supports block address translation through the use of two independent instruction and data block address translation (IBAT

and DBAT) arrays of four entries each. Effective addresses are compared simultaneously with all four entries in the BAT array during

block translation. In accordance with the PowerPC architecture, if an effective address hits in both the TLB and BAT array, the BAT

translation takes priority.

The 603e has a selectable 32 - or 64-bit - data bus and a 32-bit address bus. The 603e interface protocol allows multiple masters to

compete for system resources through a central external arbiter. The 603e provides a three-state coherency protocol that supports

the exclusive, modified, and invalid cache states. This protocol as a compatible subset of the MESI (modified/exclusive/shared/in-

valid) four-state protocol and operates coherently in systems that contain four-state caches. The 603e supports single-beat and burst

data transfers for memory accesses, and supports memory-mapped I/O.

The 603e uses an advanced, 3.3 V CMOS process technology and maintains full interface compatibility with TTL devices.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS(X)PC603EMGU/T2LN | 32-BIT, 80 MHz, RISC PROCESSOR, CBGA255 |

| TS(X)PC603EMGU2ML | 32-BIT, 80 MHz, RISC PROCESSOR, CBGA255 |

| TS(X)PC603EVAB/C4LL | 32-BIT, 120 MHz, RISC PROCESSOR, CQFP240 |

| TS(X)PC603EVAB/T5LL | 32-BIT, 133 MHz, RISC PROCESSOR, CQFP240 |

| TS(X)PC603EVGU3LL | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSXPC860SRVZQU66D | 功能描述:IC MPU POWERQUICC 66MHZ 357PBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點(diǎn):全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| TSXPCX1031 | 制造商:Schneider Electric 功能描述:CABLE TO PC SERIAL PORT (SUB-D9) 制造商:Schneider Electric 功能描述:PROGRAMMABLE CABLE 制造商:Schneider Electric 功能描述:MULTI-FUNCTION COMMUNICATION CABLE 制造商:Schneider Electric 功能描述:PROGRAMMABLE CABLE; Accessory Type:Programmable Cable; For Use With:Schneider Non-Ethernet Based Twido PLCs ;RoHS Compliant: Yes 制造商:Schneider Electric 功能描述:Programme cable for twido-nano-micro PLC |

| TSXPLP01 | 制造商:Schneider Electric 功能描述:BATTERY FOR TSX 37 制造商:Schneider Electric 功能描述:BATTERY FOR TSX 37 ;ROHS COMPLIANT: YES 制造商:Schneider Electric 功能描述:TSXPLP01 PLC replacement battery |

| TSXPLP101 | 制造商:Schneider Electric 功能描述:BATTERY TSX 37 QTY.10, TSXPLP101 |

| TSXPRGLDR | 制造商:Schneider Electric 功能描述:PROGRAM LOADER FOR 07/37 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。