- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373714 > TS68882MF25 (ATMEL CORP) CMOS Enhanced Floating-point Co-processor PDF資料下載

參數(shù)資料

| 型號(hào): | TS68882MF25 |

| 廠商: | ATMEL CORP |

| 元件分類: | 數(shù)學(xué)處理器 |

| 英文描述: | CMOS Enhanced Floating-point Co-processor |

| 中文描述: | MATH COPROCESSOR, CQFP68 |

| 封裝: | CERAMIC, QFP-68 |

| 文件頁數(shù): | 12/43頁 |

| 文件大小: | 1414K |

| 代理商: | TS68882MF25 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

12

TS68882

2119A

–

HIREL

–

04/02

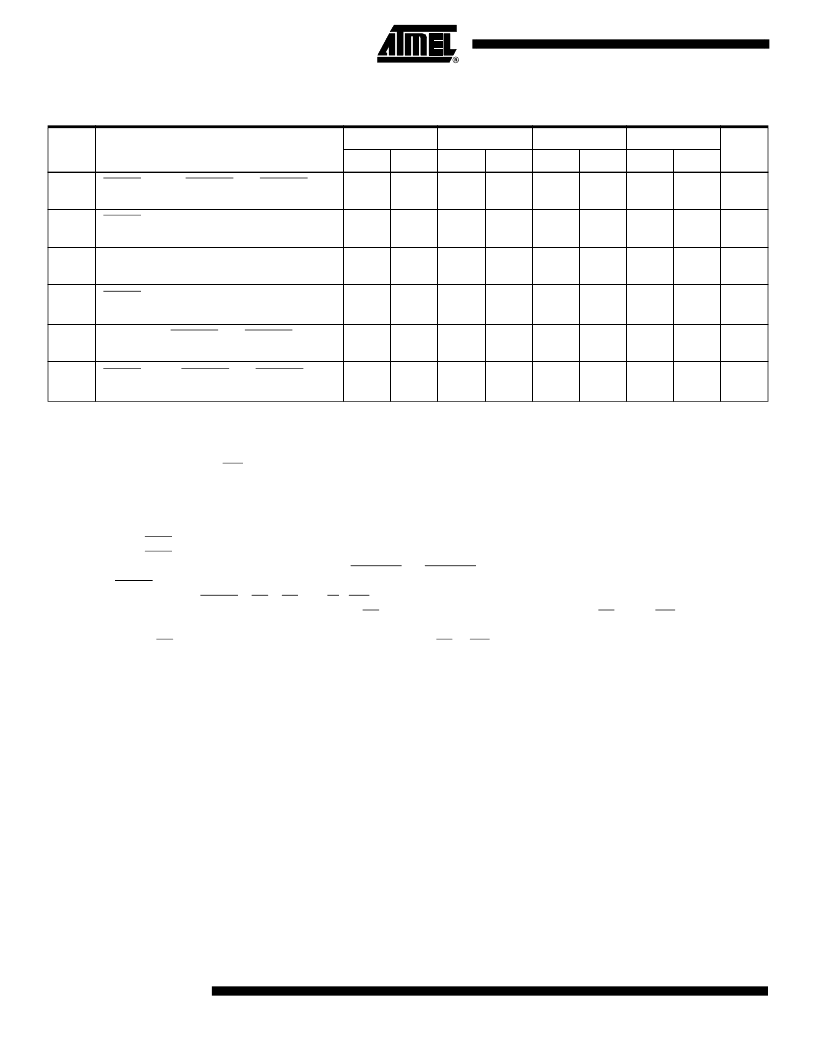

Notes:

1. Timing measurements are referenced to and from a low voltage of 0.8V and a high voltage of 2.0V, unless otherwise noted.

The voltage swing through this range should start outside, and pass through, the range such that the rise or fall will be linear

between 0.8V and 2.0V.

2. These specifications only apply if the TS68882 has completed all internal operations initiated by the termination of the previ-

ous bus cycle when DS was negated.

3. Synchronous read cycles occur only when the save or response CIR locations are read.

4. This specification only applies to systems in which back-to-back accesses (read-write or write-write) of the operand CIR can

occur. When the TS68882 is used as a co-processor to the TS68020/68030, this can occur when the addressing mode is

immediate.

5. If the SIZE pin is not strapped to either V

CC

or GND, it must have the same setup times as do addresses.

6. If the SIZE pin is not strapped to either V

CC

or GND, it must have the same hold times as do addresses.

7. This number is reduced to 5 nanoseconds if DSACK0 and DSACK1 have equal loads.

8. START is not an external signal; rather, it is the logical condition that indicates the start of an access. The logical equation for

this condition is START = CS + AS + (R/W

·

DS).

9. If a subsequent access is not a FPCP access, CS must be negated before the assertion of AS and/or DS on the non-FPCP

access. These specifications replace the old specifications 8 and 8A (the old specifications implied that in all cases, transi-

tions in CS must not occur simultaneously with transitions of AS or DS. This is not a requirement of the TS68882).

22

START false to DSACK0 and DSACK1

high impedance

(8)

70

55

55

40

ns

23

START true to clock high (synchronous

read)

(3)(8)

0

0

0

0

ns

24

Clock low to data-out valid synchronous

read)

(3)

105

80

60

45

ns

25

START true to data-out valid (synchronous

read)

(3)(8)

0

1.5

105+

2.5

1.5

80 +

2.5

1.5

60+

2.5

1.5

45-

2.5

ns

Clks

26

Clock low to DSACK0 and DSACK1

asserted (synchronous read

(3)

75

55

45

30

ns

27

START true to DSACK0 and DSACK1

asserted (synchronous read)

(3)(8)

1.5

75+

2.5

1.5

55+

2.5

1.5

45+

2.5

1.5

30-

2.5

ns

Clks

Table 7.

AC Electrical Characteristics

–

Read and Write Cycles

(1)

(Continued)

V

CC

= 5.0 V

DC

± 10%; GND = 0 V

DC;

Tc = -55

°

C/+125

°

C or Tc = -40

°

C/+85

°

C (see Figure 7, Figure 8, Figure 9)

N

°

Parameter

16.67 MHz

20 MHz

25 MHz

33.33 MHz

Unit

Min

Max

Min

Max

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68882MF33 | CMOS Enhanced Floating-point Co-processor |

| TS68882VR20 | DC-DC Converter; Supply Voltage:48V; Output Voltage:3.3V; Number of Outputs:1; Power Rating:198W; Mounting Type:PC Board; Efficiency:91%; External Depth:2.40"; External Height:0.50"; External Width:2.28"; Isolation Voltage:1500V RoHS Compliant: Yes |

| TS68882DESC01YA | CMOS Enhanced Floating-point Co-processor |

| TS68882DESC02XA | CMOS Enhanced Floating-point Co-processor |

| TS68882DESC03YA | CMOS Enhanced Floating-point Co-processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68882MF33 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:CMOS Enhanced Floating-point Co-processor |

| TS68882MFB/C16 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:CMOS Enhanced Floating-point Co-processor |

| TS68882MFB/C20 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:CMOS Enhanced Floating-point Co-processor |

| TS68882MFB/C25 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:CMOS Enhanced Floating-point Co-processor |

| TS68882MR1-33 | 制造商:e2v technologies 功能描述:TS68882MR1-33 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。