- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365955 > TS80C188EC-20 16-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | TS80C188EC-20 |

| 元件分類: | 16位微控制器 |

| 英文描述: | 16-Bit Microprocessor |

| 中文描述: | 16位微處理器 |

| 文件頁(yè)數(shù): | 52/57頁(yè) |

| 文件大?。?/td> | 585K |

| 代理商: | TS80C188EC-20 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

80C186EC/188EC, 80L186EC/188EC

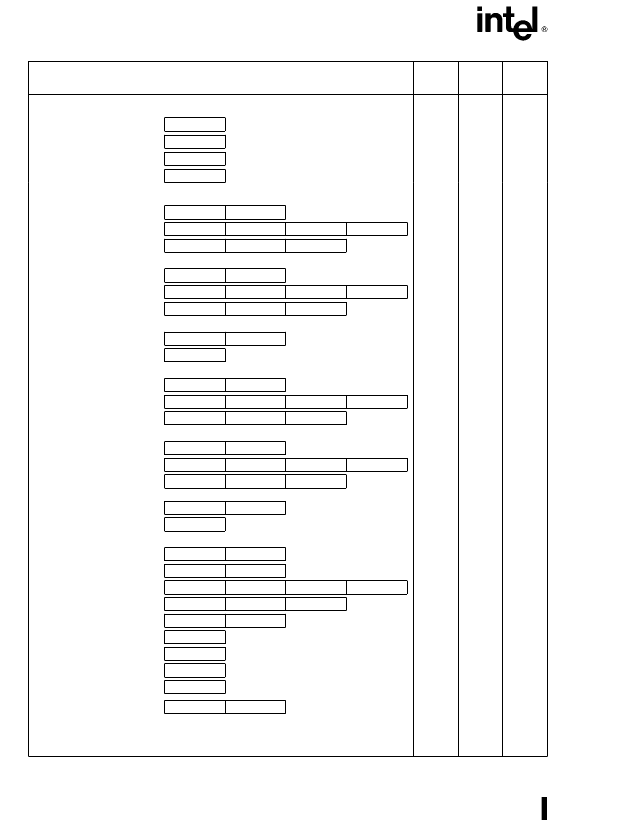

INSTRUCTION SET SUMMARY

(Continued)

Function

Format

80C186EC

Clock

Cycles

80C188EC

Clock

Cycles

Comments

DATA TRANSFER

(Continued)

SEGMENT

e

Segment Override:

CS

0 0 1 0 1 1 1 0

2

2

SS

0 0 1 1 0 1 1 0

2

2

DS

0 0 1 1 1 1 1 0

2

2

ES

0 0 1 0 0 1 1 0

2

2

ARITHMETIC

ADD

e

Add:

Reg/memory with register to either

0 0 0 0 0 0 d w

mod reg r/m

3/10

3/10

*

Immediate to register/memory

1 0 0 0 0 0 s w

mod 0 0 0 r/m

data

data if s w

e

01

4/16

4/16

*

Immediate to accumulator

0 0 0 0 0 1 0 w

data

data if w

e

1

3/4

3/4

8/16-bit

ADC

e

Add with carry:

Reg/memory with register to either

0 0 0 1 0 0 d w

mod reg r/m

3/10

3/10

*

Immediate to register/memory

1 0 0 0 0 0 s w

mod 0 1 0 r/m

data

data if s w

e

01

4/16

4/16

*

Immediate to accumulator

0 0 0 1 0 1 0 w

data

data if w

e

1

3/4

3/4

8/16-bit

INC

e

Increment:

Register/memory

1 1 1 1 1 1 1 w

mod 0 0 0 r/m

3/15

3/15

*

Register

0 1 0 0 0 reg

3

3

SUB

e

Subtract:

Reg/memory and register to either

0 0 1 0 1 0 d w

mod reg r/m

3/10

3/10

*

Immediate from register/memory

1 0 0 0 0 0 s w

mod 1 0 1 r/m

data

data if s w

e

01

4/16

4/16

*

Immediate from accumulator

0 0 1 0 1 1 0 w

data

data if w

e

1

3/4

3/4

*

8/16-bit

SBB

e

Subtract with borrow:

Reg/memory and register to either

0 0 0 1 1 0 d w

mod reg r/m

3/10

3/10

*

Immediate from register/memory

1 0 0 0 0 0 s w

mod 0 1 1 r/m

data

data if s w

e

01

4/16

4/16

*

Immediate from accumulator

0 0 0 1 1 1 0 w

data

data if w

e

1

3/4

3/4

*

8/16-bit

DEC

e

Decrement

Register/memory

1 1 1 1 1 1 1 w

mod 0 0 1 r/m

3/15

3/15

*

Register

0 1 0 0 1 reg

3

3

CMP

e

Compare:

Register/memory with register

0 0 1 1 1 0 1 w

mod reg r/m

3/10

3/10

*

Register with register/memory

0 0 1 1 1 0 0 w

mod reg r/m

3/10

3/10

*

Immediate with register/memory

1 0 0 0 0 0 s w

mod 1 1 1 r/m

data

data if s w

e

01

3/10

3/10

*

Immediate with accumulator

0 0 1 1 1 1 0 w

data

data if w

e

1

3/4

3/4

8/16-bit

NEG

e

Change sign register/memory

1 1 1 1 0 1 1 w

mod 0 1 1 r/m

3/10

3/10

*

AAA

e

ASCII adjust for add

0 0 1 1 0 1 1 1

8

8

DAA

e

Decimal adjust for add

4

4

AAS

e

ASCII adjust for subtract

0 0 1 1 1 1 1 1

7

7

DAS

e

Decimal adjust for subtract

0 0 1 0 1 1 1 1

4

4

MUL

e

Multiply (unsigned):

1 1 1 1 0 1 1 w

mod 100 r/m

Register-Byte

Register-Word

Memory-Byte

Memory-Word

26–28

35–37

32–34

41–43

26–28

35–37

32–34

41–43

*

Shaded areas indicate instructions not available in 8086/8088 microsystems.

NOTE:

*

Clock cycles shown for byte transfers, for word operations, add 4 clock cycles for all memory transfers.

52

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS80L186EC13 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| TS80C186EC13 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| TS80C186EC20 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

| TS80L186EC-13 | 16-Bit Microprocessor |

| TS80L188EC13 | MICROPROCESSOR|16-BIT|CMOS|QFP|100PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS80C188XL10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TS80C188XL12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|16-BIT|CMOS|QFP|80PIN|PLASTIC |

| TS80C188XL-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| TS80C188XL20 | 功能描述:IC MPU 16-BIT 5V 20MHZ 80-MQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| TS80C194 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。