- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄272328 > TS80C31X2-VJBB (ATMEL CORP) 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | TS80C31X2-VJBB |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 73/83頁 |

| 文件大小: | 8336K |

| 代理商: | TS80C31X2-VJBB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

85

7707F–AVR–11/10

AT90USB82/162

Note:

1. n = 3, 2, 1or 0.

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

12.0.2

External Interrupt Control Register B – EICRB

Bits 7..0 – ISC71, ISC70 - ISC41, ISC40: External Interrupt 7 - 4 Sense Control Bits

The External Interrupts 7 - 4 are activated by the external pins INT7:4 if the SREG I-flag and the

corresponding interrupt mask in the EIMSK is set. The level and edges on the external pins that

activate the interrupts are defined in Table 12-3. The value on the INT7:4 pins are sampled

before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one

clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an inter-

rupt. Observe that CPU clock frequency can be lower than the XTAL frequency if the XTAL

divider is enabled. If low level interrupt is selected, the low level must be held until the comple-

tion of the currently executing instruction to generate an interrupt. If enabled, a level triggered

interrupt will generate an interrupt request as long as the pin is held low.

Note:

1. n = 7, 6, 5 or 4.

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

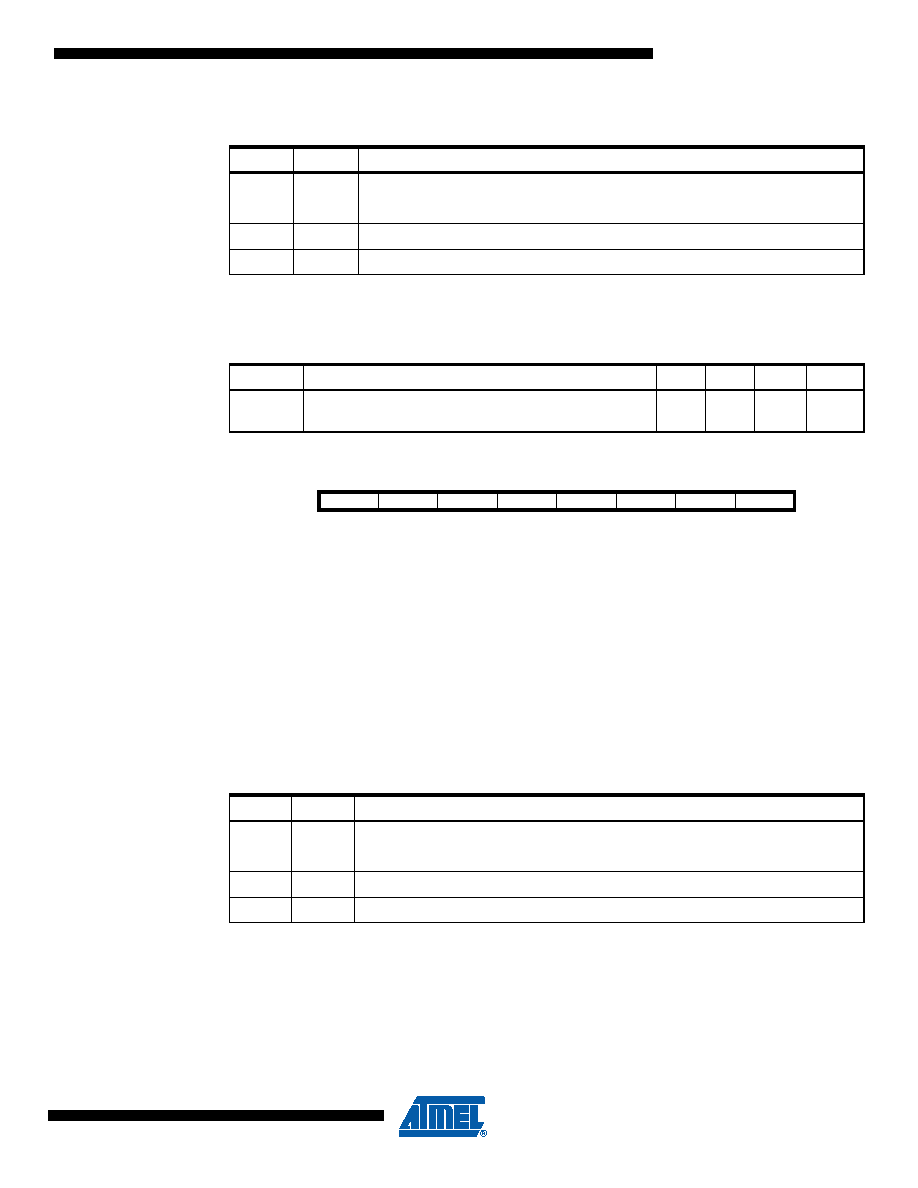

Table 12-1.

Interrupt Sense Control(1)

ISCn1

ISCn0

Description

0

The low level of INTn generates an interrupt request.

0

1

Any edge of INTn generates asynchronously an interrupt request.

1

0

The falling edge of INTn generates asynchronously an interrupt request.

1

The rising edge of INTn generates asynchronously an interrupt request.

Table 12-2.

Asynchronous External Interrupt Characteristics

Symbol

Parameter

Condition

Min

Typ

Max

Units

tINT

Minimum pulse width for asynchronous

external interrupt

50

ns

Bit

7654

3

2

1

0

ISC71

ISC70

ISC61

ISC60

ISC51

ISC50

ISC41

ISC40

EICRB

Read/Write

R/WR/W

Initial Value

0000

0

Table 12-3.

Interrupt Sense Control

ISCn1

ISCn0

Description

0

The low level of INTn generates an interrupt request.

0

1

Any logical change on INTn generates an interrupt request

1

0

The falling edge between two samples of INTn generates an interrupt request.

1

The rising edge between two samples of INTn generates an interrupt request.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC80C31-16KAD | 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 |

| TSC80C31-40JDB | 8-BIT, 40 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-12LFR | 8-BIT, 12 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-20LFD | 8-BIT, 20 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-36KB | 8-BIT, 36 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS80C31X2-VLAB | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless |

| TS80C31X2-VLAD | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless |

| TS80C31X2-VLAR | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless |

| TS80C31X2-VLBB | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless |

| TS80C31X2-VLBD | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless |

發(fā)布緊急采購,3分鐘左右您將得到回復。