- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC106AVG83CE MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSPC106AVG83CE |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁數(shù): | 14/40頁 |

| 文件大?。?/td> | 569K |

| 代理商: | TSPC106AVG83CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

14

TSPC106

2102B

–

HIREL

–

02/02

Multiple Processor

Signals

When a system implementation uses more than one 60x processor, nine of the internal

L2 cache controller signals change their functions.

Note that in a multi-processor system, with the exception of the bus grant, bus request

and data bus grant signals, all of the 60x processor interface signals are shared by all

60x processors.

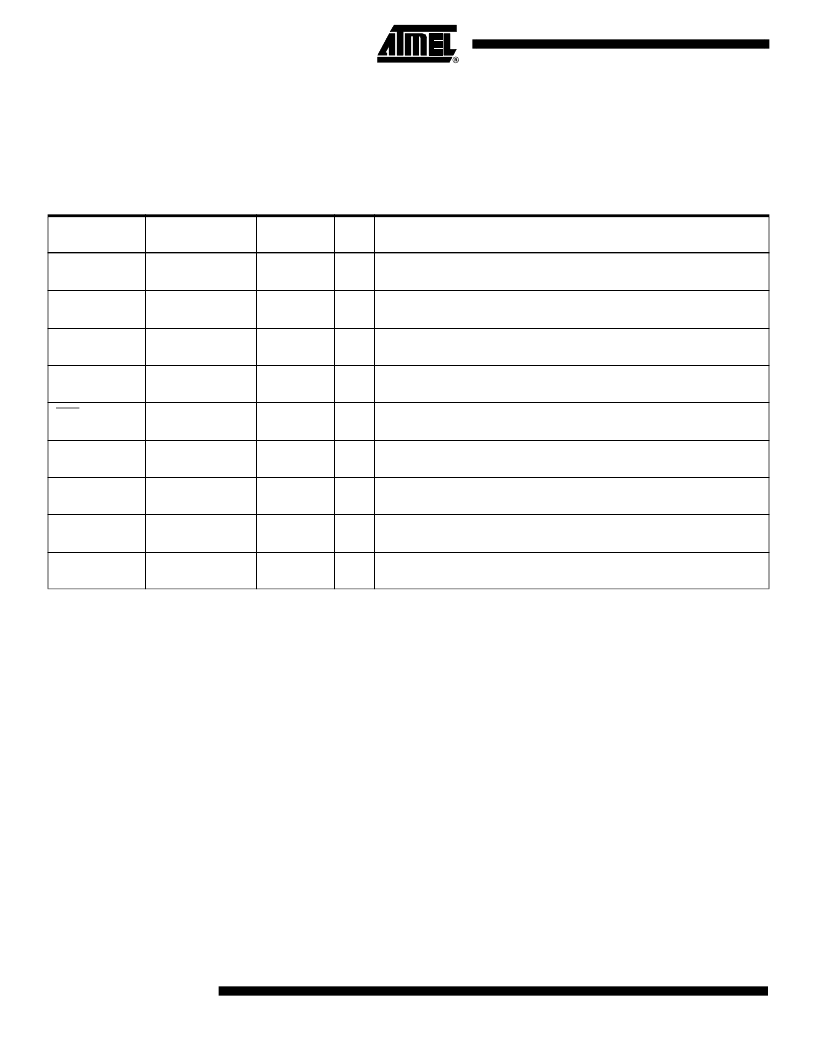

Table 5.

Multiple Processor Signals

Signal

Signal Name

Numberof

Pins

I/O

Signal Description

BG1

DIRTY_OUT

Bus grant 1

1

O

Indicates that processor 1 may, with the proper qualification, begin a

60x bus transaction and assume mastership of the address bus.

BG2

TWE

Bus grant 2

1

O

Indicates that processor 2 may, with the proper qualification, begin a

60x bus transaction and assume mastership of the address bus.

BG3

DCS

Bus grant 3

1

O

Indicates that processor 3 may, with the proper qualification, begin a

60x bus transaction and assume mastership of the address bus.

BR1

DIRTY_IN

Bus request 1

1

I

Indicates that processor 1 requires mastership of the 60x bus for a

transaction.

BR2

TV

Bus request 2

1

I

Indicates that processor 2 requires mastership of the 60x bus for a

transaction.

BR3

BA0

Bus request 3

1

I

Indicates that processor 3 requires mastership of the 60x bus for a

transaction.

DBG1

TOE

Data bus grant 1

1

O

Indicates that processor 1 may, with the proper qualification, assume

mastership of the 60x data bus.

DBG2

DWE0

Data bus grant 2

1

O

Indicates that processor 2 may, with the proper qualification, assume

mastership of the 60x data bus.

DBG3

DWE1

Data bus grant 3

1

O

Indicates that processor 3 may, with the proper qualification, assume

mastership of the 60x data bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVG83CG | MEMORY CONTROLLER |

| TSPC106AVGS66CE | MEMORY CONTROLLER |

| TSPC106AVGS66CG | MEMORY CONTROLLER |

| TSPC106AVGS83CE | MEMORY CONTROLLER |

| TSPC106AVGS83CG | MEMORY CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC106AVG83CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PCI Bus Bridge Memory Controller 66-83 MHz |

| TSPC106AVGS66CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS66CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS83CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。