- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC603RMGU12LC MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC603RMGU12LC |

| 元件分類: | 微處理器 |

| 英文描述: | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| 中文描述: | 微處理器| 32位|的CMOS | BGA封裝| 255PIN |陶瓷 |

| 文件頁數(shù): | 18/42頁 |

| 文件大?。?/td> | 961K |

| 代理商: | TSPC603RMGU12LC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

18

TSPC603R

2125A–12/01

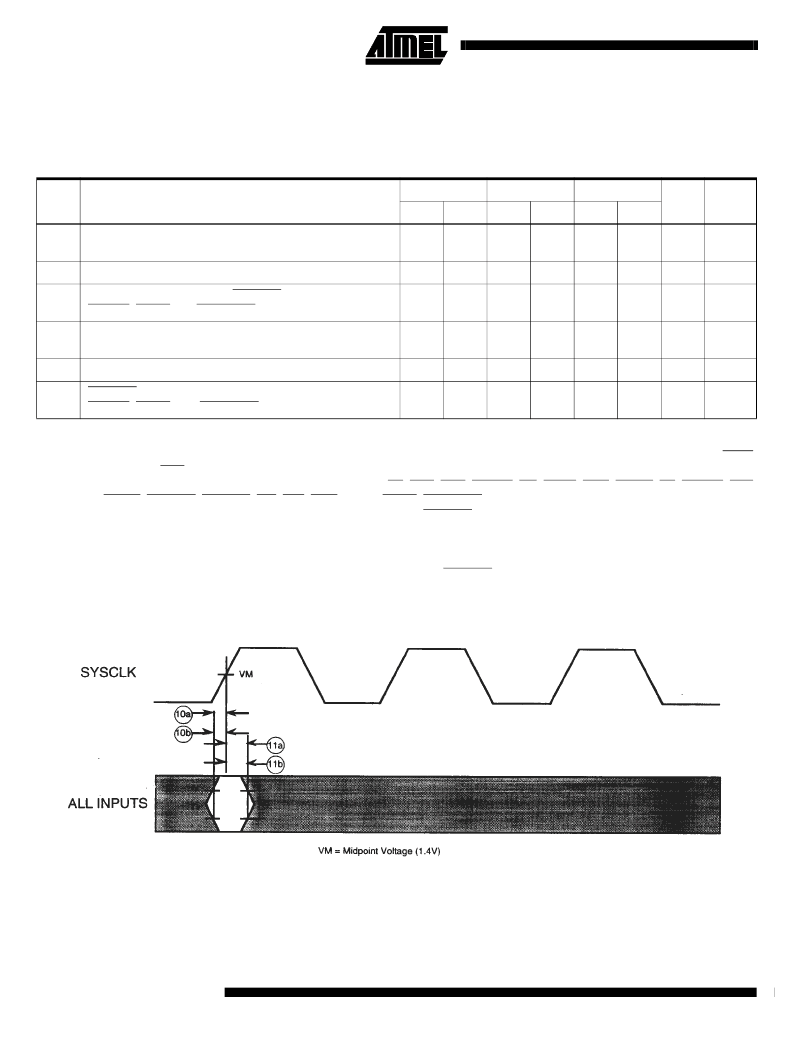

Table 11 provides the input AC timing specifications for the 603r as defined in Figure 6 and

Figure 7.

Notes:

1. All input specifications are measured from the TTL level (0.8 or 2.0V) of the signal in question to the 1.4V of the rising edge

of the input SYSCLK. Both input and output timings are measured at the pin. See Figure 7.

2. Address/data/transfer attribute input signals are composed of the following: A[0-31], AP[0-3], TT[0-4], TC[0-1], TBST,

TSIZ[0-2], GBL, DH[0-31], DL[0-31], DP[9-7].

3. All other input signals are composed of the following: TS, ABB, DBB, ARTRY, BG, AACK, DBG, DBWO, TA, DRTRY, TEA,

DBDIS, HRESET, SRESET, INT, SMI, MCP, TBEN, QACK, TLBISYNC.

4. The setup and hold time is with respect to the rising edge of HRESET. See Figure 7.

5. t

sysclk

is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied

by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.

6. These values are guaranteed by design, and are not tested.

7. This specification is for configuration mode only. Also note that HRESET must be held asserted for a minimum of 255 bus

clocks after the PLL relock time (100 μs) during the power-on reset sequence.

Figure 6.

Input Timing Diagram

Table 11.

Input AC Timing Specifications

V

dd

= A

V

dd

= 2.5V

±

5%; O

V

dd

= 3.3

±

5%V dc, GND = 0V dc, -55

°

C

≤

T

C

≤

125

°

C

Num

Characteristics

166,200 MHz

233,266 MHz

300 MHz

Unit

Note

Min

Max

Min

Max

Min

Max

10a

Address/data/transfer attribute inputs valid to SYSCLK

(input setup)

2.5

-

2.5

-

2.5

-

ns

2

10b

All other inputs valid to SYSCLK (input setup)

4.0

-

3.5

-

3.5

-

ns

3

10c

Mode select inputs valid to HRESET (input setup) (for

DRTRY, QACK and TLBISYNC)

8

-

8

-

8

-

t

sysclk

4,5,6,

7

11a

SYSCLK to address/data/transfer attribute inputs invalid

(input hold)

1.0

-

1.0

-

1.0

-

ns

2

11b

SYSCLK to all other inputs invalid (input hold)

1.0

-

1.0

-

1.0

-

ns

3

11c

HRESET to mode select inputs invalid (input hold) (for

DRTRY, QACK, and TLBISYNC)

0

-

0

-

0

-

ns

4,6,7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC603RMGU14LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMGU6LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMGU8LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RVG10LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RVG12LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC603RMGU14LC | 制造商:e2v technologies 功能描述:MPU PID7T- RISC 64BIT 0.29UM 300MHZ 3.3V 255CBGA - Trays |

| TSPC603RMGU6LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMGU8LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RVA8LC | 功能描述:IC MPU 32BIT 8MHZ 240CERQUAD RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點(diǎn):全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| TSPC603RVAB/Q8L | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。