- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365990 > TSPC750AVGSU12LH Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC750AVGSU12LH |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 21/44頁(yè) |

| 文件大小: | 870K |

| 代理商: | TSPC750AVGSU12LH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

21

TSPC750A/740A

2128A–HIREL–01/02

Notes:

1. For60xbussignals,thereferenceisOV

DD

whileL2OV

DD

isthereferencefortheL2bussignals.

2. Excludestestsignals(LSSD_MODE,L1_TSTCLK,L2_TSTCLK)andIEEE1149.1boundaryscan(JTAG)signals.

3. Capacitanceisperiodicallysampledratherthan100%tested.

4. TheleakageismeasuredfornominalOV

DD

andV

DD

,orbothOV

DD

andV

DD

mustvaryinthesamedirection(forexample,

bothOV

DD

andV

DD

varybyeither+5%or-5%).

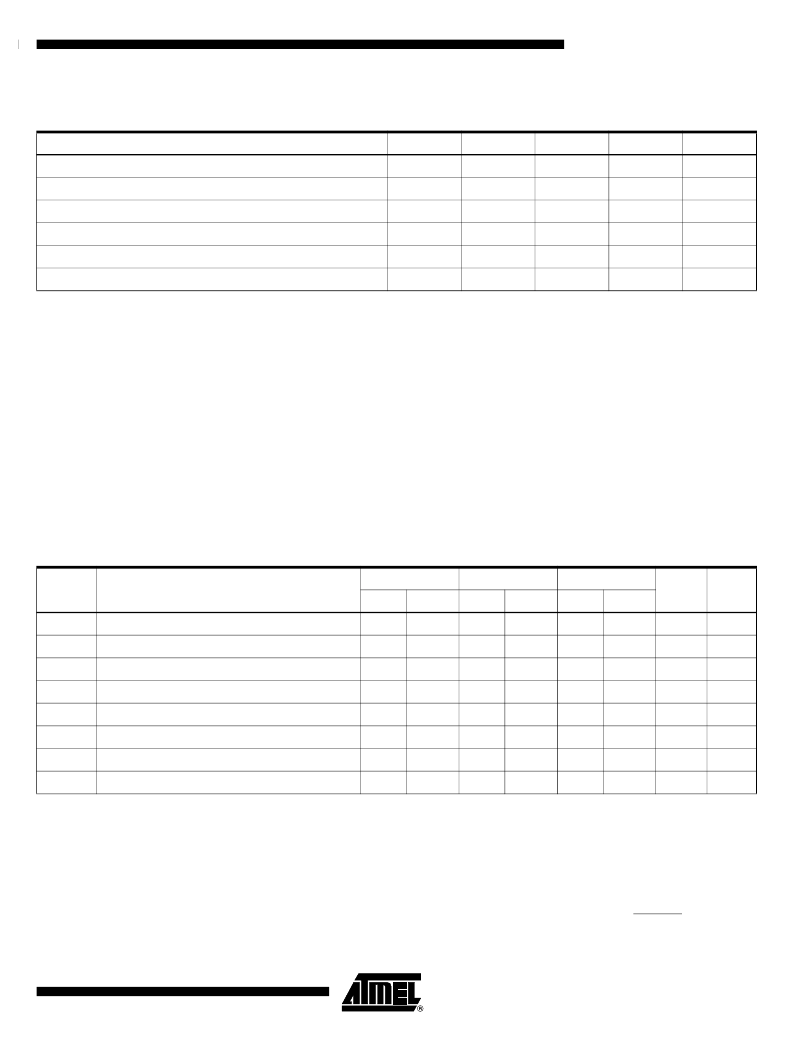

DynamicCharacteristics

Afterfabrication,partsaresortedbymaximumprocessorcorefrequencyasshownin

“ClockACSpecifications”andtestedforconformancetotheACspecificationsforthat

frequency.Thesespecificationsarefor200,233,and266MHzprocessorcorefrequen-

cies.Theprocessorcorefrequencyisdeterminedbythebus(SYSCLK)frequencyand

thesettingsofthePLL_CFG[0-3]signals.Partsaresoldbymaximumprocessorcore

frequency.

ClockACSpecifications

Table9providestheclockACtimingspecificationsasdefinedinFigure9.

Notes:

1.

Caution

:TheSYSCLKfrequencyandPLL_CFG[0-3]settingsmustbechosensuchthattheresultingSYSCLK(bus)fre-

quency,CPU(core)frequency,andPLL(VCO)frequencydonotexceedtheirrespectivemaximumorminimumoperating

frequencies.RefertothePLL_CFG[0-3]signaldescriptionin“PLLConfiguration,”forvalidPLL_CFG[0-3]settings

2. RiseandfalltimesfortheSYSCLKinputaremeasuredfrom0.4to2.4V.

3. Timingisguaranteedbydesignandcharacterization.

4. Thetotalinputjitter(shorttermandlongtermcombined)mustbeunder

±

150ps.

5. Relocktimingisguaranteedbydesignandcharacterization.PLL-relocktimeisthemaximumamountoftimerequiredfor

PLLlockafterastableV

DD

andSYSCLKarereachedduringthepower-onresetsequence.Thisspecificationalsoapplies

whenthePLLhasbeendisabledandsubsequentlyre-enabledduringsleepmode.AlsonotethatHRESETmustbeheld

assertedforaminimumof255busclocksafterthePLL-relocktimeduringthepower-onresetsequence.

SYSCLKInputLowVoltage

CV

IL

GND

0.4

V

InputLeakageCurrent,V

IN

=OV

DD

I

in

-

30

μA

1,2

Hi-Z(off-state)LeakageCurrent,V

IN

=OV

DD

I

TSI

-

30

μA

1,2,4

OutputHighVoltage,I

OH

=

-6mA

V

OH

2.4

-

V

OutputLowVoltage,I

OL

=6mA

V

OL

-

0.4

V

Capacitance,V

IN

=0V,f=1MHz

C

in

-

5.0

pF

2,3

Table8.

DCElectricalSpecifications

V

DD

=AV

DD

=L2AV

DD

=2.6V

DC

±

100mV,OV

DD

=L2OV

DD

=3.3±

5%V

DC

,GND=0V

DC

,-55

≤

T

j

<125

°

C

Characteristic

Symbol

Min

Max

Unit

Notes

Table9.

ClockACTimingSpecifications

V

DD

=AV

DD

=L2AV

DD

=2.6V

DC

±

100mV,OV

DD

=L2OV

DD

=3.3±5%V

DC

,GND=0V

DC

,-55

≤

T

j

<125

°

C

Num

Characteristic

200MHz

233MHz

266MHz

Unit

Notes

Min

Max

Min

Max

Min

Max

ProcessorFrequency

150

200

150

233

150

266

MHz

VCOFrequency

300

400

300

466

300

533

MHz

SYSCLKFrequency

25

83.3

25

83.3

25

83.3

MHz

1

1

SYSCLKCycleTime

12

40

12

40

12

40

ns

2,3

SYSCLKRiseandFallTime

-

2

-

2

-

2

ns

2

4

SYSCLKDutyCycleMeasuredat1.4V

40

60

40

60

40

60

%

3

SYSCLKJitter

-

±

150

-

±

150

-

±

150

ps

4

InternalPLLRelockTime

-

100

-

100

-

100

μs

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC750AVGSU8LE | Microprocessor |

| TSPC750AVGSU8LH | Microprocessor |

| TSXPC750AMG12LH | Microprocessor |

| TSXPC750AMG8LE | Microprocessor |

| TSXPC750AMG8LH | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC750AVGSU8LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TSPC750AVGSU8LH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TSPC750AVGU/T10LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TSPC750AVGU/T10LH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TSPC750AVGU/T12LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。