- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376431 > UPD75206 (NEC Corp.) 4-BIT SINGLE-CHIP MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | UPD75206 |

| 廠商: | NEC Corp. |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| 中文描述: | 4位單片機(jī) |

| 文件頁(yè)數(shù): | 12/62頁(yè) |

| 文件大小: | 489K |

| 代理商: | UPD75206 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

12

μ

PD75206

4.

μ

PD75206 ARCHITECTURE AND MEMORY MAP

The

μ

PD75206 has the following three architectural features.

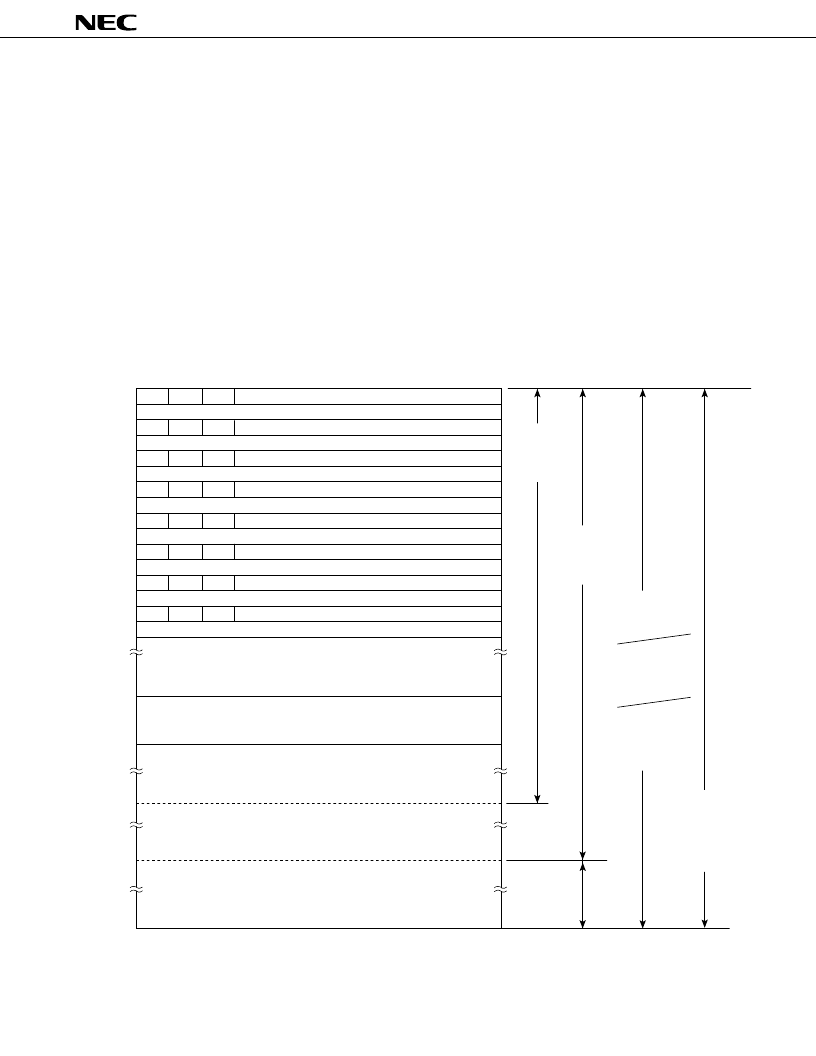

Data memory bank configuration:

Static RAM (320 words x 4 bits)

Display data memory (49 words x 4 bits)

Peripheral hardware (128 x 4 bits)

General register bank configuration: 8 x 4 banks (Operated in 4 bits)

4 x 4 banks (Operated in 8 bits)

Memory mapped I/O

Figures 4-1, 4-2 shows memory maps of

μ

PD75206.

Remarks

In all cases other than those listed above, branch to the address with only the lower 8 bits of the PC

changed is enabled by BR PCDE and BR PCXA instructions.

MBE

RBE

MBE

RBE

MBE

RBE

MBE

RBE

MBE

RBE

MBE

RBE

MBE

RBE

MBE

6

INTBT/INT4 Start Address

INTBT/INT4 Start Address

INT0 Start Address

INT0 Start Address

INT1 Start Address

INT1 Start Address

Internal Reset Start Address (Most Significant 5 Bits)

Internal Reset Start Address (Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

(Most Significant 5 Bits)

(Least Significant 8 Bits)

INTSIO Start Address

INTSIO Start Address

INTT0 Start Address

INTT0 Start Address

INTTPG Start Address

INTTPG Start Address

INTKS Start Address

INTKS Start Address

GETI Instruction Reference Table

0002H

0004H

0006H

0008H

000AH

000CH

000EH

0000H

0020H

007FH

0080H

07FFH

0800H

0FFFH

1000H

177FH

Address

7

RBE

0

CALLF

!faddr

Instruction

Entry Address

BRCB

!caddr

Instruction

Branch Address

BR !addr

Instruction

Branch Address

CALL !addr

Instruction

Subroutine Entry

Address

BR $addr Instruction

Relative Branch

Address

(-15 to -1 and +2 to +16)

Branch Destination

Address and

Subroutine Entry

Address to be Set

by GETI Instruction

0

0

0

0

0

0

0

0

5

Fig. 4-1 Program Memory Map

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD75206CW | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208GF | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208CW | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD753208GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD753016AGC-P29-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75304GF-407-3B9 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75306G182 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。